El DAC5681 es un convertidor de digital a analógico (DAC) 1.0 GSPS de 16 bits con entradas de datos LVDS de banda ancha y una referencia de voltaje interno. El DAC5681 ofrece una excelente linealidad y rendimiento de ruido.

Convertidor de digital a analógico (DAC) de 16 bits, 1.0 GSPS

El DAC5681 es un convertidor de digital a analógico (DAC) 1.0 GSPS de 16 bits con entradas de datos LVDS de banda ancha y una referencia de voltaje interno. El DAC5681 ofrece una excelente linealidad y rendimiento de ruido.

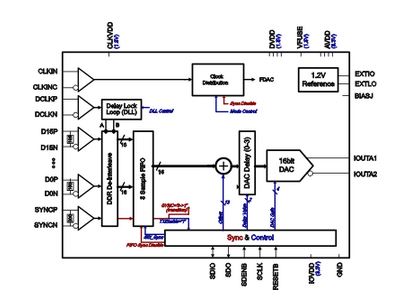

El DAC5681 integra un puerto LVDS de banda ancha con terminación en chip para proporcionar una transferencia de datos 1.0 GSPS completa al DAC y una EMI más baja que las interfaces de datos CMOS tradicionales. Un bucle de bloqueo de retardo (DLL) en el chip simplifica la interfaz LVDS al proporcionar control de desviación del reloj de datos de entrada LVDS.

La arquitectura de dirección de corriente DAC5681 consta de una matriz segmentada de interruptores de sumidero de corriente que dirigen hasta 20 mA de corriente a gran escala a nodos de salida complementarios. Una referencia precisa de voltaje en el chip se compensa con la temperatura para proporcionar un voltaje de referencia estable de 1,2 V. Opcionalmente, también se puede utilizar una referencia externa.

El DAC5681 funciona en el rango de temperatura industrial de -40 °C a 85 °C y viene en un paquete QFN de 64 pines. Este dispositivo es pin actualizable a otros miembros de la familia, el DAC5681Z y el DAC5682Z. Tanto el DAC5681Z de un solo canal como el DAC5682Z de dos canales ofrecen interpolación 2x/4x y PLL de multiplicación de reloj opcionales.

característica

- Convertidor de digital a analógico (DAC) de 16 bits

- Tasa de actualización de 1.0 GSPS

- Bus de datos LVDS de entrada de banda ancha de 16 bits

- 8 entradas de muestra FIFO

- Bucle de bloqueo de retardo en chip

- alto rendimiento

- 73 dBc ACLR WCDMA TM1 a 180 MHz

- Referencia de 1,2 V en chip

- Salida escalable diferencial: 2-20 mA

- Paquete: 64 pines 9x9mm QFN