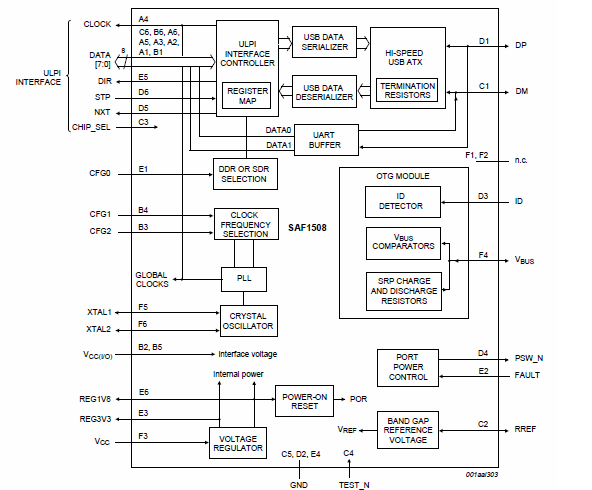

El SAF1508BET es un transceptor UTMI+ Low Pin Interface (ULPI) Universal Serial Bus (USB) que cumple totalmente con la Universal Serial Bus Specification Rev. 2.0, On-The-Go Supplement to USB 2.0 Specification Rev. 1.3 y UTMI+ Low Pin Interface . (ULPI) Especificación Rev. 1.1.

El SAF1508BET puede transmitir y recibir datos USB a alta velocidad (480 Mbit/s), velocidad completa (12 Mbit/s) y baja velocidad (1,5 Mbit/s) y ofrece un frente de capa física optimizado para pines. Termina las conexiones a hosts USB, periféricos o controladores On-The-Go (OTG) con interfaces ULPI de velocidad de datos única (SDR) o velocidad de datos dual (DDR). El SAF1508BET puede enviar y recibir señales UART de forma transparente.

Permite que un circuito integrado específico de la aplicación (ASIC) USB, un dispositivo lógico programable (PLD) o cualquier conjunto de chips del sistema se conecte con la capa física USB a través de una interfaz digital síncrona de 8 pines (DDR) o 12 pines (SDR). Ser capaz de interactuar. .

El SAF1508BET se puede conectar a dispositivos con voltajes de E/S digitales que van desde 1,4 V a 1,95 V.

El SAF1508BET se ofrece en el paquete TFBGA36.

Características y Beneficios

- Totalmente compatible con:

- USB: especificación de bus serie universal Rev. 2.0

- OTG: suplemento sobre la marcha de la especificación USB 2.0 Rev. 1.3

- ULPI: UTMI+ Low Pin Interface (ULPI) Especificación Rev. 1.1 Interfaz a un host USB, periférico o núcleo OTG. Optimizado para sistema ASIC con enlace ULPI integrado

Una solución frontal física USB de alta velocidad completa que admite alta velocidad (480 Mbit/s), velocidad completa (12 Mbit/s) y baja velocidad (1,5 Mbit/s):

- Resistencia de terminación de alta velocidad integrada de 45 Ω, resistencia pull-up de dispositivo de velocidad máxima de 1,5 kΩ y resistencia de terminación de host de 15 kΩ

- Convertidores paralelo/serie y serie/paralelo integrados para transmisión y recepción

- Reciba datos USB hasta ±500 ppm con reloj USB y recuperación de datos

- Inserción de bits de relleno durante la transmisión y descarte de bits de relleno durante la recepción

- Codificación y decodificación invertida sin retorno a cero (NRZI)

- Admite reinicio de bus, suspensión, reanudación y reconocimiento rápido de apretón de manos (chirrido)

- Una interfaz física USB OTG completa compatible con el protocolo de negociación de host (HNP) y el protocolo de solicitud de sesión (SRP):

- Admite bomba de carga externa o interruptor de alimentación VBUS externo

- Control total sobre las resistencias de terminación USB

- Línea de datos y método de solicitud de sesión de pulso VBUS

- Comparador de tensión VBUS integrado

- Detector de cable interno (ID)

- Integración flexible del sistema y muy bajo consumo de energía

- Rango de entrada de alimentación de 3,0 V a 4,5 V

- El regulador de voltaje interno proporciona 2,7 V o 3,3 V y 1,8 V

- Admite voltajes de E/S de interfaz de 1,4 V a 1,95 V.Minimice la diafonía con pines de suministro de voltaje de E/S independientes

- El modo de apagado apaga el regulador interno cuando VCC (I/O) no está presente o el pin CHIP_SEL no está activo.

- La corriente de funcionamiento típica es de 13 mA a 32 mA (según la velocidad del USB y la utilización del bus)

- El consumo de energía VCC típico es de 70 μA en modo de suspensión y de 0,5 μA en modo de apagado.

- La interfaz ULPI de tres estados con pin CHIP_SEL permite la reutilización del bus por otras aplicaciones

- Interfaz compatible con ULPI altamente optimizada

- Interfaz de 60 MHz, 8 pines o 12 pines entre el núcleo y el transceptor (incluido el bus DDR de 4 bits o el bus SDR de 8 bits)

- Interfaz DDR o SDR seleccionable por pin

- Admite configuración de reloj de salida de 60 MHz

- Bucle de enganche de fase integrado (PLL) compatible con frecuencias de cristal o de reloj de 13 MHz, 19,2 MHz, 24 MHz o 26 MHz

- Pin seleccionable de cristal o frecuencia de reloj

- Conjunto de registro compatible con ULPI totalmente programable

- Modo serial de baja velocidad o velocidad completa de 3 pines o 6 pines

- Circuito interno de reinicio de encendido (POR)

- Interfaz UART:

- Admite señalización UART transparente en pines DP y DM para aplicaciones de accesorios UART

- Señalización UART de 2,7 V en pines DP y DM

- Transición al modo UART mediante configuración de registro

- Afirme STP o cambie el pin CHIP_SEL para salir del modo UART

- Rango de temperatura de funcionamiento de grado industrial completo de -40 °C a +85 °C

- Cumplimiento ESD:

- JESD22-A114D, modelo de cuerpo humano de contacto de 2 kV (HBM)

- JESD22-A115-A, modelo de máquina de 200 V (MM)

- JESD22-C101C, modelo de dispositivo de carga (CDM) de 500 V

- Disponible en paquetes diminutos TFBGA36 (3,5 mm X 3,5 mm) que cumplen con la Restricción de Sustancias Peligrosas (RoHS), libres de halógenos y sin plomo

solicitud

Este producto USB de NXP solo puede usarse en aplicaciones automotrices. No se permite la integración o el uso de productos USB de NXP fuera de las aplicaciones automotrices y es bajo el propio riesgo de la empresa. Usted acepta indemnizar completamente a NXP por cualquier daño causado por dicha incorporación o uso.