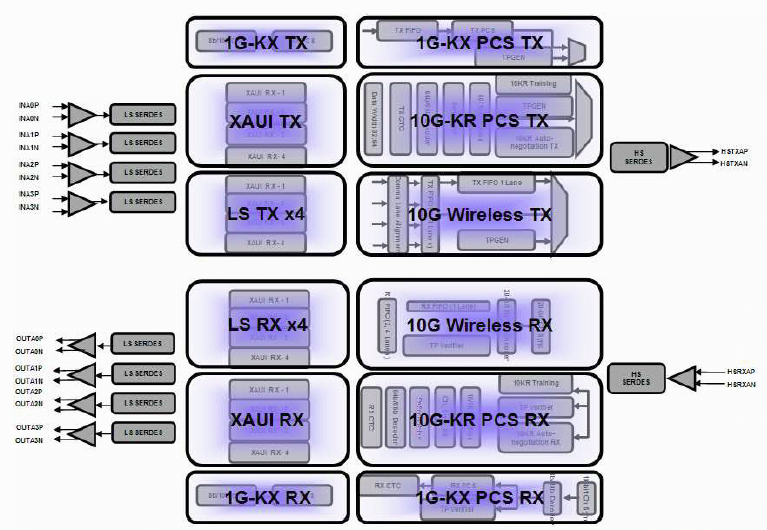

El TLK10034 es un transceptor multivelocidad de cuatro canales diseñado para su uso en sistemas de transmisión de datos punto a punto bidireccional de alta velocidad. Este dispositivo admite tres modos principales. Se puede utilizar como transceptor XAUI a 10GBASE-KR, como serializador/deserializador 8b/10b multitasa 4:1, 2:1 o 1:1 de uso general, o en modo 1G-KX.El TLK10034 es un transceptor multivelocidad de cuatro canales diseñado para su uso en sistemas de transmisión de datos punto a punto bidireccional de alta velocidad. Este dispositivo admite tres modos principales. Se puede utilizar como transceptor XAUI a 10GBASE-KR, como serializador/deserializador 8b/10b multitasa 4:1, 2:1 o 1:1 de uso general, o en modo 1G-KX.

Mientras opera en modo 10GBASE-KR, el TLK10034 realiza la serialización del flujo de datos XAUI codificado 8B/10B proporcionado en la entrada de datos del lado de baja velocidad (LS). Los datos codificados 8B/10B serializados se presentan en la salida del lado de alta velocidad (HS) en formato codificado 64B/66B. De manera similar, el TLK10034 realiza la deserialización del flujo de datos codificados 64B/66B presentado a la entrada de datos del lado rápido. Los datos 64B/66B deserializados se mostrarán en formato 8B/10B en la salida de menor velocidad. Este modo es compatible con el entrenamiento de enlaces y la corrección de errores de reenvío (FEC) para aplicaciones de longitud extendida.

Mientras opera en el modo SERDES Genérico, el TLK10034 realiza una serialización 2:1 y 4:1 del flujo de datos codificados 8B/10B presentado a la entrada de datos del lado de baja velocidad (LS). Los datos codificados 8B/10B serializados se presentan en la salida del lado de alta velocidad (HS). De manera similar, el TLK10034 realiza una deserialización 1:2 y 1:4 del flujo de datos codificados 8B/10B presentado a la entrada de datos del lado de alta velocidad. Los datos codificados 8B/10B deserializados aparecen en la salida del lado de baja velocidad. Dependiendo de la relación de serialización/deserialización, la tasa de datos en el lado inferior oscila entre 0,5 Gbps y 5 Gbps, mientras que la tasa de datos en el lado superior oscila entre 1 Gbps y 10 Gbps. También se admite el modo de reprogramación 1:1, pero la velocidad está limitada a 1 Gbps a 5 Gbps.

El TLK10034 también admite el modo 1G-KX (1,25 Gbps) con funcionalidad PCS (CTC). Este modo se puede habilitar mediante el aprovisionamiento de software o la negociación automática. Se admiten velocidades de datos de hasta 3,125 Gbps cuando se utiliza el aprovisionamiento de software.

Tanto las entradas como las salidas de datos del lado lento y del lado rápido son tipos de lógica de modo de corriente diferencial (CML) con resistencias de terminación incorporadas.

El TLK10034 ofrece esquemas de reloj flexibles para soportar una variedad de operaciones. Estos incluyen soporte para cronometrar con un reloj sin fluctuaciones externas recuperado del lado de alta velocidad. El dispositivo también puede realizar la compensación de tolerancia del reloj (CTC) en los modos 10GBASE-KR y 1G-KX, lo que permite el reloj asincrónico.

El TLK10034 proporciona modos de bucle invertido de lado bajo y lado alto para fines de autocomprobación y diagnóstico del sistema.

El TLK10034 incluye un generador de patrones y un verificador útil para probar el sistema. El dispositivo admite la generación y verificación de varios patrones de prueba pseudoaleatorios PRBS, alto, bajo, mixto, CRPAT largo/corto, CJPAT, KR y generación de onda cuadrada. Los tipos de patrones admitidos por los lados lento y rápido dependen del modo de funcionamiento seleccionado.

El TLK10034 integra la detección de pérdida de señal (LOS) en los lados rápido y lento. LOS se afirma bajo la condición de que la oscilación del voltaje diferencial de entrada sea menor que el umbral de afirmación de LOS.

En el modo 10GBASE-KR, la alineación de carriles para cada canal se logra mediante el esquema de alineación de carriles XAUI estándar. En el modo SERDES Genérico, la alineación de los carriles laterales de baja velocidad para cada canal se logra a través de un esquema único de alineación de carriles. Los dispositivos asociados del enlace ascendente deben implementar un esquema de alineación de carriles para el funcionamiento correcto del enlace. La operación de enlace normal se reanuda solo después de que se completa el ajuste de carril.

Los cuatro canales TLK10034 son completamente independientes. Pueden operar con diferentes relojes de referencia, diferentes tasas de datos y diferentes relaciones de serialización/deserialización.

El lado de baja velocidad del TLK10034 es ideal para interactuar con FPGA o ASIC capaces de procesar flujos de datos en serie de baja velocidad. El lado de alta velocidad es ideal para interactuar con sistemas remotos a través de interfaces de fibra óptica, cable eléctrico o backplane. El TLK10034 admite el funcionamiento con módulos ópticos SFP y SFP+ y sistemas de backplane compatibles con 10GBASE-KR.

*característica*

* Transceptor multivelocidad de cuatro canales

* Compatible con los estándares Ethernet 10GBASE-KR, XAUI y 1GBASE-KX

* Admite todas las velocidades de datos CPRI y OBSAI de hasta 10 Gbps

* Admite la operación SERDES de velocidad múltiple hasta una velocidad de datos de 10.3125 Gbps

*Hasta 5 Gbps en el lado de alta y baja velocidad

* E/S CML diferencial para el lado rápido y lento

* Interfaz a backplane, pasivo y

* Cable de cobre activo o módulo óptico SFP+

* Reloj de referencia seleccionable por canal

* Múltiples opciones de reloj de salida

* Función de bucle invertido en los lados rápido y lento

* Operación de reprogramación de datos de soporte

* Admite PRBS, CRPAT, CJPAT, patrones de frecuencia alta/baja/mixta y KR

* Generación y verificación de patrones pseudoaleatorios, generación de ondas cuadradas

* Dos suministros: 1,0 V, nominal 1,5 o 1,8 V

* Sin requisitos de secuencia de potencia

* Permite transmitir desacentuación y recibir ecualización adaptativa

* Rango extendido de backplane/cable en los lados de alta y baja velocidad

* Columpio de salida de transmisión programable en ambos lados rápido y lento

* Detección de pérdida de señal (LOS)

* Admite entrenamiento de enlace 10G-KR, corrección de errores hacia adelante y negociación automática

* Compatibilidad con paquetes gigantes

* JTAG; interfaz de prueba IEEE 1149.1/1149.6

* Estándar de la industria MDIO Artículo 45 y Artículo 22 interfaz de control

* Tecnología CMOS avanzada de 65nm

* Temperatura ambiente industrial de funcionamiento (-40 °C a 85 °C)

* Consumo de energía: 825 mW por canal (nominal)

* Paquete del dispositivo: 19 mm x 19 mm, PBGA de 324 pines, paso de bola de 1 mm