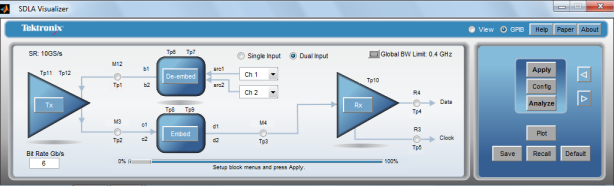

Tektronix, Inc. anunció un nuevo paquete de software visualizador de análisis de enlace de datos en serie (SDLA Visualizer) para los osciloscopios de rendimiento de Tektronix, incluida la serie DPO/DSA/MSO70000. Los diseñadores que trabajan en la próxima generación de estándares seriales de alta velocidad pueden usar SDLA Visualizer para especificar enlaces, separar componentes de rutas medidas, simular componentes de enlaces virtuales, aplicar ecualización y diseñar líneas de transmisión para datos seriales. puntos en la parte superior. sistema, módulo o chipset.Tektronix, Inc. anunció un nuevo paquete de software visualizador de análisis de enlace de datos en serie (SDLA Visualizer) para los osciloscopios de rendimiento de Tektronix, incluida la serie DPO/DSA/MSO70000. Los diseñadores que trabajan en la próxima generación de estándares seriales de alta velocidad pueden usar SDLA Visualizer para especificar enlaces, separar componentes de rutas medidas, simular componentes de enlaces virtuales, aplicar ecualización y diseñar líneas de transmisión para datos seriales. puntos en la parte superior. sistema, módulo o chipset.

Los diseñadores que caracterizan, depuran y cumplen con la capa física de los buses de alta velocidad en las computadoras, las comunicaciones y la memoria pueden cerrar con confianza la brecha entre el comportamiento del modelado y el rendimiento real de la integridad de la señal con SDLA Visualizer.can. Esto reduce significativamente el tiempo del ciclo de diseño y acelera la toma de decisiones en proyectos de diseño críticos.

Brian Reich, Gerente General, Osciloscopios de Rendimiento en Tektronix. “A medida que los estándares de datos y memoria en serie se vuelven más rápidos y complejos, los diseñadores necesitan herramientas nuevas, más poderosas y flexibles para caracterizar con precisión las señales bajo prueba”. transiciones perfectas entre los entornos de caracterización, cumplimiento y depuración”.

Desde USB 3.0 en adelante, las tecnologías seriales modernas requieren un software de análisis de enlace avanzado que considere todos los componentes de la red, el equipo de medición y los modelos de IP específicos del silicio. Del mismo modo, los diseñadores integrados que necesitan implementar enlaces de alta velocidad en sus sistemas se enfrentan al desafío de probar las señales en los puntos de prueba previstos y necesitan filtrar los reflejos y otros efectos para ver la verdadera señal.

Para satisfacer estas necesidades, SDLA Visualizer proporciona un modelado completo de 4 puertos, teniendo en cuenta la impedancia de salida del transmisor, la impedancia de entrada del osciloscopio y del receptor, y la impedancia del canal y del dispositivo para representar la señal con la mayor fidelidad posible. Esto se logra considerando los términos de reflexión, pérdida de inserción y acoplamiento mutuo de cada elemento en el enlace. También permite a los usuarios validar y depurar parámetros S de elementos de enlace individuales bajo demanda, ahorrando tiempo a los usuarios y brindando visibilidad por elemento o en cualquier punto de prueba dentro del enlace.

Otro desafío importante es la validación del modelo vinculado. SDLA facilita esta tarea con un conjunto completo de gráficos que incluyen respuesta de frecuencia, respuesta de fase y gráficos de los 16 parámetros S. Además de su facilidad de uso, SDLA proporciona una interfaz de usuario única y común para definir todos los componentes del enlace al tiempo que permite a los usuarios administrar múltiples puntos de prueba en lugar de crear diferentes modelos de enlace para cada punto de prueba. La combinación de SDLA Visualizer con el software DPOJET Jitter and Eye Analysis permite a los usuarios validar los resultados de ojo y jitter en múltiples puntos de prueba simultáneamente, brindando confianza de que el modelo está configurado correctamente.

*Integración del modelo IBIS AMI*

Para facilitar la manipulación de modelos de IP específicos de silicio, SDLA Visualizer va más allá de admitir técnicas de ecualización de receptor de referencia y puede incorporar algoritmos de ecualización de receptor y recuperación de reloj específicos del proveedor para ayudar en la configuración y definición del modelo de enlace. A menudo se basan en el estándar de modelado de interfaz de modelado algorítmico de IBIS para enlaces de capa física en serie (PHY) (IBIS-AMI).

“Los diseñadores de sistemas usan modelos IBIS-AMI para diseñar y verificar enlaces de alta velocidad antes de la fabricación de PCB, pero la precisión del modelo es una preocupación importante”. Software de simulación EDA para “Los clientes necesitan una manera fácil de correlacionar modelos y mediciones y realizar análisis hipotéticos en tiempo real en el hardware del laboratorio. Establece la base para una función de laboratorio de integridad de señal emblemática”.

*disponibilidad*

El nuevo software SDLA Visualizer estará disponible para que los clientes lo descarguen en todo el mundo a fines del primer trimestre de 2013. Póngase en contacto con su administrador de cuentas de Tektronix para obtener más información.