ARM y Cadence cumplen sus promesas de escalamiento de potencia y rendimiento a 16 nanómetros y anuncian detalles de la asociación para implementar el primer procesador ARM® Cortex®-A57 en el proceso de fabricación FinFET de 16 nanómetros (nm) de TSMC. Este chip de prueba se implementó utilizando un flujo completo de Cadence RTL hasta la aprobación, una plataforma de diseño personalizado Cadence Virtuoso, bibliotecas de celdas estándar ARM Artisan® y macros de memoria de TSMC.ARM y Cadence cumplen sus promesas de escalamiento de potencia y rendimiento a 16 nanómetros y anuncian detalles de la asociación para implementar el primer procesador ARM® Cortex®-A57 en el proceso de fabricación FinFET de 16 nanómetros (nm) de TSMC. Este chip de prueba se implementó utilizando un flujo completo de Cadence RTL hasta la aprobación, una plataforma de diseño personalizado Cadence Virtuoso, bibliotecas de celdas estándar ARM Artisan® y macros de memoria de TSMC.

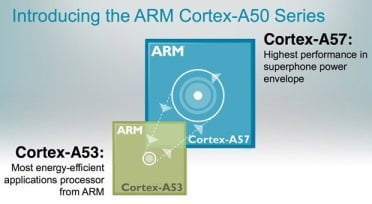

El procesador Cortex-A57 es el procesador de mayor rendimiento de ARM hasta la fecha, basado en la nueva arquitectura ARMv8 y diseñado para aplicaciones informáticas, de redes y móviles que requieren alto rendimiento con bajo consumo de energía. La tecnología FinFET de 16nm de TSMC es un avance clave que permite el escalado continuo de la tecnología de procesos a tamaños de características por debajo de los 20nm. Este chip de prueba es una colaboración desarrollada utilizando soluciones personalizadas, digitales y de aprobación para la tecnología de proceso FinFET de Cadence, con varias innovaciones y optimizaciones conjuntas entre procesos de fabricación, IP de diseño y herramientas de diseño.

“Tener éxito en la vanguardia de la innovación requiere una colaboración más estrecha que nunca. Diseñar SoC que incorporen procesadores avanzados como el Cortex-A57 y usar IP física creada para procesos FinFET Necesitamos la experiencia de nuestros socios para optimizar nuestra implementación”, dijo Tom Cronk , vicepresidente ejecutivo y gerente general de la división de procesadores de ARM. “Nuestra innovación conjunta permite a nuestros clientes acelerar sus ciclos de desarrollo de productos y aprovechar los procesos de vanguardia y la propiedad intelectual”.

El proceso de 16 nm que utiliza la tecnología FinFET introdujo nuevos desafíos que requirieron un importante desarrollo nuevo de herramientas de diseño. Nuevas reglas de diseño, extracción RC para transistores 3D, mayor complejidad de interconexión y modelos de resistencia, bibliotecas de celdas cuantificadas, caracterización de bibliotecas que admiten nuevos modelos de transistores y patrones dobles en más capas, son algunos de los desafíos abordados en Cadence Custom. Productos digitales y de firma.

“Este hito importante fue un desafío en todos los frentes, ya que requirió que los ingenieros de ARM, Cadence y TSMC trabajaran como un equipo unificado”, dijo el Dr. Chi-Ping Hsu, vicepresidente senior de I + D, Silicon Realization Group, Cadence. “Nuestro enfoque colectivo y nuestro compromiso con la innovación permiten a los clientes diseñar SoC de bajo consumo y alto rendimiento utilizando tecnologías de diseño, procesos e IP de última generación”.