El PCKV857 es un búfer de retraso cero de alto rendimiento, baja asimetría y baja fluctuación diseñado para operación de 2,5 V VDD y 2,5 V AVDD y niveles de entrada y salida de datos diferenciales.

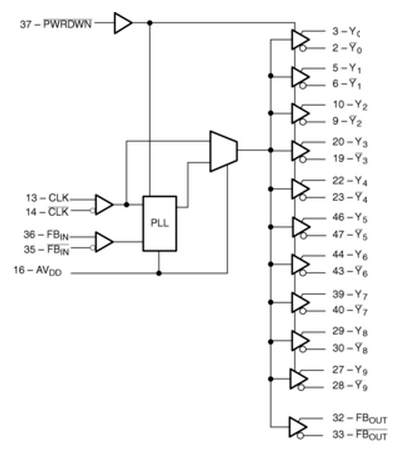

El PCKV857 es un búfer de retardo cero que distribuye un par de entrada de reloj diferencial (CLK, CLK) a 10 pares de salida de reloj diferencial (Y).[0:9]Y[0:9]) y un par diferencial de salidas de reloj de retroalimentación (FBOUT, FBOUT). Las salidas de reloj están controladas por entradas de reloj (CLK, CLK), relojes de retroalimentación (FBIN, FBIN) y entrada de fuente de alimentación analógica (AVDD). Cuando PWRDWN es alto, la salida cambiará en fase y frecuencia con CLK. Cuando PWRDWN es bajo, todas las salidas se deshabilitan a un estado de alta impedancia (tres estados) y el PLL se apaga (modo de baja potencia). Además, cuando la frecuencia de entrada cae por debajo de 20 MHz, el dispositivo entra en modo de bajo consumo. Un circuito de detección de frecuencia de entrada detecta una condición de baja frecuencia y después de aplicar una señal de entrada > 20 MHz, el circuito de detección vuelve a encender el PLL y habilita la salida.

Cuando AVDD está conectado a tierra, el PLL se apaga y se omite con fines de prueba. PCKV857 también puede rastrear el reloj de espectro ensanchado para reducir la EMI.

El PCKV857 presenta operación de 0 a +70 Cel.

*Características y Beneficios*

* Las pruebas de clasificación ESD se realizan de acuerdo con el estándar JEDEC JESD22. La protección supera los 2000 V según HBM según el método A114.

* La prueba de enganche es según el estándar JEDEC JESD78 sobre 100mA.

* Optimizado para distribución de reloj en aplicaciones SDRAM DDR (Double Data Rate) de acuerdo con las especificaciones JEDEC.

* Distribución de reloj diferencial de 1 a 10

* Sesgo muy bajo (< 100 ps) y jitter (< 100 ps)

* Funciona de 2,2 V a 2,7 V AV DD y de 2,3 V a 2,7 V VDD

* Entrada y salida de reloj de interfaz SSTL_2

* Entrada de señal de control CMOS

* En modo de prueba, habilite el búfer mientras deshabilita PLL

* Modo de apagado de baja corriente

* Tolerancia del reloj de entrada de espectro ensanchado

* Proporciona una solución DDR completa cuando se usa con SSTL16877 o SSTV16857

* Diseñado para aplicaciones DDR 200 y 266 DIMM

*Disponible en paquetes TSSOP-48, TVSOP-48 y VFBGA56 (8 sin conexión)