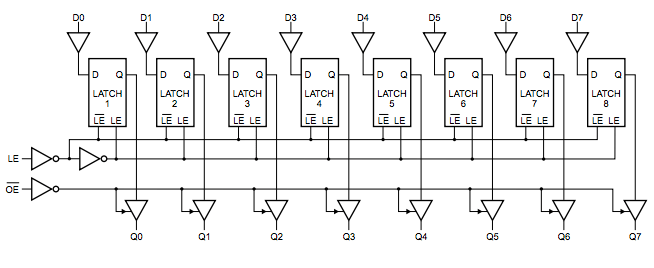

El 74LVC573A consta de ocho cerrojos transparentes de tipo D con entradas individuales de tipo D para cada cerrojo y salidas verdaderas de tres estados para aplicaciones orientadas al bus. Las entradas Latch Enable (LE) y Output Enable (OE) son comunes a todos los latches internos.

Cuando LE es ALTO, los datos en la entrada Dn están bloqueados. En este estado el pestillo es transparente. Es decir, la salida del latch cambia cada vez que cambia la entrada D correspondiente. Cuando LE está en BAJO, el pestillo almacena la información que estaba presente en la entrada D un tiempo de configuración antes de que LE pasara de ALTO a BAJO.

Cuando OE es BAJO, el contenido de los ocho latches está disponible en las salidas. Cuando OE es ALTO, la salida está en un estado desactivado de alta impedancia. La actividad en la entrada OE no afecta el estado del pestillo. Las entradas se pueden controlar desde dispositivos de 3,3 V o 5 V. Cuando está deshabilitado, se pueden aplicar hasta 5,5 V a la salida. Estas características permiten que estos dispositivos se utilicen como traductores en aplicaciones mixtas de 3,3 V o 5 V. El 74LVC573A es funcionalmente igual que el 74LVC373A, pero tiene un pinout diferente.

*característica*

* Entrada/salida tolerante a 5 V para interfaz con lógica de 5 V

* El rango de tensión de alimentación es de 1,2 a 3,6 V

* CMOS bajo consumo de energía

* Interfaz directa con nivel TTL

*Alta impedancia cuando VCC=0V

* Arquitectura de pinout de flujo continuo