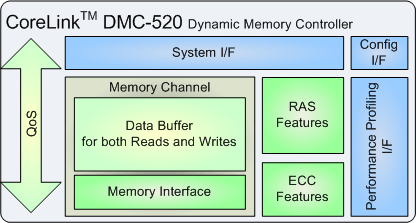

La serie CoreLinkTM 500 presenta el controlador de memoria dinámica CoreLink DMC-520 de quinta generación, diseñado específicamente para proporcionar la mejor solución para aplicaciones empresariales, incluidos servidores e infraestructura de red. CoreLink DMC-520 se conecta directamente a la red coherente de caché CoreLink CCN-504 mediante la especificación AMBA® 5 CHI (Coherent Hub Interface). CoreLink DMC-520 proporciona una interfaz de alto ancho de banda para compartir memoria fuera del chip, como DDR3, DDR3L y DDR4 DRAM.El CoreLink DMC-520 es el controlador de memoria de quinta generación de ARM. El CoreLink DMC-520 está diseñado para satisfacer las necesidades de los sistemas empresariales basados en los productos de red coherentes con caché de ARM. El CoreLink DMC-520 es una parte clave del esquema de calidad de servicio (QoS) de extremo a extremo de ARM, que contiene funcionalidad distribuida a través de los controladores de interconexión y memoria.

Las características de RAS (confiabilidad, disponibilidad, capacidad de servicio) de clase empresarial, como ECC para DRAM x72, seguridad TrustZone y QoS de extremo a extremo, son componentes integrales de este nuevo controlador de memoria. CoreLink DMC-520 utiliza una interfaz DFI para permitir la integración con PHY estándar de la industria.

*característica*

* Alto ancho de banda, baja latencia DMC-520

* Interfaz del sistema: 1 para conexión directa a productos CCN utilizando la especificación AMBA® 5 CHI (Coherent Hub Interface)

* Ancho de datos del sistema: 128 bits

* Configuración: a través de la interfaz APB

* Interfaz de memoria: 1 interfaz de memoria que se conecta a DRAM a través de la interfaz DFI

* Tipos de memoria: DDR3, DDR3(L) y DDR4

* Ancho de memoria: x72 bit DRAM

* ECC: SECDED o ECC mejorado

* QoS: algoritmo de programación basado en QoS, ruta sin bloqueo a DRAM a través de CCN