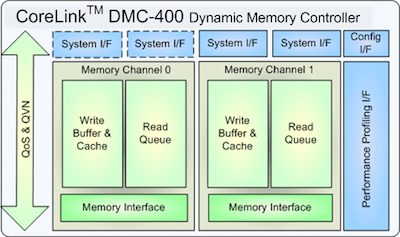

El controlador de memoria dinámica CoreLinkTM DMC-400 ofrece soporte de múltiples canales para conectarse a la especificación completa de DRAM DDR3, DDR2 o LPDDR2. CoreLink DMC-400 brinda una excelente integración con los productos de interconexión CoreLink 400 (CCI-400 y NIC-400) a través de las interfaces AMBA3 AXI o AMBA 4, compartiendo mecanismos de QoS y administración de energía.El controlador de memoria dinámica CoreLinkTM DMC-400 ofrece soporte de múltiples canales para conectarse a la especificación completa de DRAM DDR3, DDR2 o LPDDR2. CoreLink DMC-400 brinda una excelente integración con los productos de interconexión CoreLink 400 (CCI-400 y NIC-400) a través de las interfaces AMBA3 AXI o AMBA 4, compartiendo mecanismos de QoS y administración de energía.

El CoreLink DMC-400 es el controlador de memoria de cuarta generación de ARM. El CoreLink DMC-400 está diseñado para satisfacer las necesidades de los diversos maestros en su sistema mientras brinda el máximo ancho de banda de su DRAM. CoreLink DMC-400 es una parte clave del esquema de calidad de servicio (QoS) de extremo a extremo de ARM que incluye funciones distribuidas tanto en el controlador de interconexión como en el controlador de memoria.

*característica*

* Interfaz del sistema: 1, 2 o 4 interfaces ACE-Lite (se pueden conectar ACE-Lite, AXI4 o AXI3)

* Ancho de datos del sistema: ACE-Lite de 64, 128 o 256 bits

* Configuración: interfaz APB

* Interfaz de memoria: 1 o 2 interfaces de memoria para conectarse a canales independientes de DRAM a través de la interfaz DFI

* Tipo de memoria: DDR3, DDR2 o LPDDR2

* Ancho de memoria: DRAM de 16, 32 o 64 bits por interfaz de memoria

* ECC: ECC SECDED opcional compatible con DRAM

* QoS: algoritmo de programación basado en QoS, QVN (red virtual) para evitar bloqueos

* Bajo consumo de energía: Admite todos los modos de alimentación de DRAM y permite la activación jerárquica del reloj en los DMC.