El 74HC/HCT160 es un dispositivo CMOS Si Gate de alta velocidad que es compatible con clavijas con Low Power Schottky TTL (LSTTL). Se especifican de acuerdo con la Norma JEDEC No. 7A. El 74HC/HCT160 es un contador de décadas síncrono y preestablecido con arrastre interno que se puede utilizar para contar a alta velocidad. La operación síncrona se logra cronometrando todos los flip-flops simultáneamente con el flanco ascendente del reloj (CP).

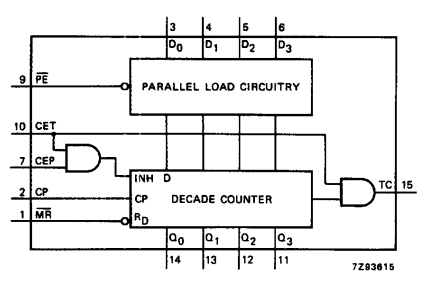

Las salidas del contador (Q0-Q3) se pueden preestablecer a nivel ALTO o BAJO. Un nivel BAJO en la entrada de habilitación paralela (PE) deshabilita la operación de conteo y carga datos en las entradas de datos (D0-D3) en el contador en el flanco ascendente del reloj (si la configuración está completa). se cumplen los requisitos de tiempo de retención para PE). El preajuste ocurre independientemente del nivel de las entradas de habilitación de conteo (CEP y CET).

Un nivel BAJO en la entrada de reinicio maestro (MR) establece las cuatro salidas de los flip-flops (Q0-Q3) en un nivel BAJO (por lo tanto, se proporciona una función de borrado asíncrono). El arrastre simplifica la conexión en serie de contadores en cascada. Ambas entradas de habilitación de conteo (CEP y CET) deben estar en ALTO para contar. La entrada CET se alimenta hacia adelante para habilitar la salida de conteo de terminales (TC). La salida TC así habilitada produce un pulso de salida ALTA de duración aproximadamente igual a la salida de nivel ALTO de Q0. Este pulso se puede utilizar para habilitar la siguiente etapa en cascada. La frecuencia de reloj máxima para el contador en cascada está determinada por el retardo de propagación de CP a TC y el tiempo de configuración de CEP a CP de acuerdo con la siguiente fórmula:

fmax= (1) / (tP (max)(CP a TC) + tSU(CEP a CP) )

característica

- Conteo y carga sincrónicos

- Dos entradas de habilitación de conteo para cascada de n bits

- reloj activado por flanco positivo

- Restablecimiento asíncrono

- Capacidad de salida: estándar

- Categoría ICC: MSI

solicitud

- televisor

- conjunto de sonido para el hogar

- sistema multimedia

- Todos los sistemas de audio alimentados por red

- audio del coche (amplificador)