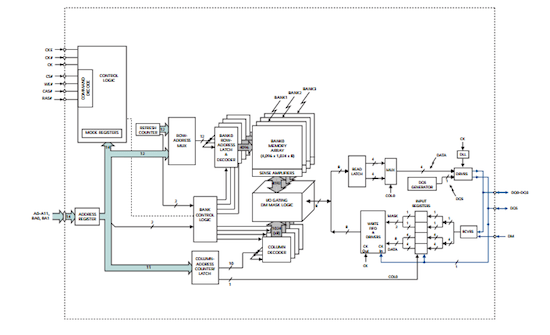

Micron Technology presenta DDR SDRAM a través de onlinecomponents.com. El dispositivo utiliza una arquitectura de doble velocidad de datos para lograr un funcionamiento de alta velocidad. Además, la arquitectura de tasa de datos doble de este dispositivo es esencialmente una arquitectura de captación previa 2n con una interfaz diseñada para transferir dos palabras de datos por ciclo de reloj en los pines de E/S. Un acceso de lectura o escritura DDR SDRAM es una transferencia de datos de 1 ciclo de reloj de 2 n bits de ancho en el núcleo DRAM interno y dos ciclos correspondientes de 1/2 reloj de n bits de ancho en la E / S. Consta de ciclos de transferencia de datos. alfiler.

Micron Technology presenta DDR SDRAM a través de onlinecomponents.com. El dispositivo utiliza una arquitectura de doble velocidad de datos para lograr un funcionamiento de alta velocidad. Además, la arquitectura de tasa de datos doble de este dispositivo es esencialmente una arquitectura de captación previa 2n con una interfaz diseñada para transferir dos palabras de datos por ciclo de reloj en los pines de E/S. Un acceso de lectura o escritura DDR SDRAM es una transferencia de datos de 1 ciclo de reloj de 2 n bits de ancho en el núcleo DRAM interno y dos ciclos correspondientes de 1/2 reloj de n bits de ancho en la E / S. Consta de ciclos de transferencia de datos. alfiler.

Una luz estroboscópica bidireccional de datos (DQS) se envía externamente junto con los datos para su uso en la captura de datos en el receptor. DQS es una luz estroboscópica enviada por DDR SDRAM durante las lecturas y por el controlador de memoria durante las escrituras. DQS está alineado en los bordes para los datos de LECTURA y alineado en el centro para los datos de ESCRITURA. Los productos x16 tienen dos luces estroboscópicas de datos, una para el byte bajo y otra para el byte alto.

DDR SDRAM opera con relojes diferenciales (CK y CK#). El cruce de CK en ALTO y CK# en BAJO se denomina flanco positivo de CK. Los comandos (señales de dirección y control) se registran en cada flanco positivo de CK. Los datos de entrada se registran en ambos bordes de DQS y los datos de salida se referencian en ambos bordes de DQS y ambos bordes de CK.

Los accesos de lectura y escritura a DDR SDRAM están orientados a ráfagas. El acceso comienza en la ubicación seleccionada y continúa en la secuencia programada a través del número programado de ubicaciones. El acceso comienza con el registro de un comando ACTIVO, posiblemente seguido por un comando de LECTURA o ESCRITURA. Los bits de dirección registrados con el comando ACTIVE se utilizan para seleccionar el banco y la fila para acceder. Los bits de dirección registrados con el comando READ o WRITE se utilizan para seleccionar el banco y la ubicación de la columna inicial para los accesos en ráfaga.

DDR SDRAM ofrece longitudes de ráfaga de lectura o escritura programables de 2, 4 u 8 ubicaciones. Puede habilitar la función PRECARGA AUTOMÁTICA para proporcionar una precarga automática de filas que comienza al final de un acceso de ráfaga.

Al igual que la SDR SDRAM estándar, la arquitectura multibanco canalizada de la DDR SDRAM permite el funcionamiento simultáneo y proporciona un ancho de banda altamente efectivo al ocultar los tiempos de precarga y activación de las filas.

Se proporcionan un modo de actualización automática y un modo de ahorro de energía. Todas las entradas son compatibles con el estándar JEDEC de SSTL_2. Todas las salidas de la opción de accionamiento completo son compatibles con SSTL_2, Clase II.

característica

- VDD = +2,5 V ±0,2 V, VDDQ = +2,5 V ±0,2 V

- VDD = +2,6 V ±0,1 V, VDDQ = +2,6 V ±0,1 V (DDR400)

- Luz estroboscópica de datos bidireccional (DQS) enviada/recibida con datos, es decir, captura de datos síncrona de origen (x16 tiene 2 – 1 por byte)

- Arquitectura interna canalizada de doble velocidad de datos (DDR).2 accesos de datos por ciclo de reloj

- Entradas de reloj diferencial (CK y CK#)

- Comando ingresado en cada flanco CK positivo

- DQS está alineado con los bordes de los datos en READ. ESCRIBIR datos y centrado

- DLL para alinear las transiciones DQ y DQS a CK

- Cuatro bancos internos para operación simultánea

- Máscara de datos (DM) para enmascarar datos de escritura (x16 tiene dos, uno por byte)

- Longitud de ráfaga programable: 2, 4 u 8

- Modo de actualización automática y modo de actualización automática

- TSOP de plomo más largo para mejorar la confiabilidad (OCPL)

- 2.5 E/S (compatible con SSTL_2)

- Opción de precarga automática simultánea admitida