En los últimos meses, hemos estado analizando lo que se necesita para escribir un buen código RTL. Hemos visto cómo escribir RTL controlado por registros, cómo escribir procesos combinatorios y cómo escribir máquinas de estado.

En los últimos meses, hemos estado analizando lo que se necesita para escribir un buen código RTL. Hemos visto cómo escribir RTL controlado por registros, cómo escribir procesos combinatorios y cómo escribir máquinas de estado. Todo este trabajo supone que tiene una herramienta de síntesis que convierte RTL correctamente escrito en puertas.

Esto hace que las herramientas de síntesis sean una parte importante de su flujo de trabajo. Comprender cómo funciona la síntesis y cómo funciona es esencial para nosotros. Este artículo cubre los conceptos básicos de la composición.

Lo primero que debe saber es que la síntesis de hardware no es una compilación de software. Cuando escribimos software, rara vez pensamos en cómo el compilador traduce objetos, estructuras de datos, tipos y funciones al lenguaje ensamblador. Supongo que funciona lo suficiente como para ejecutar el código en la plataforma de destino. De hecho, no es una buena idea pensar demasiado en la compilación. Porque es difícil controlar la compilación en tu propio estilo de codificación.

No ocurre lo mismo con la composición. La síntesis de hardware es muy sensible a cómo se escribe el RTL. Se puede crear hardware dramáticamente diferente escribiendo el RTL de diferentes maneras. (Para ver un ejemplo de cómo controlar la síntesis con su estilo de codificación, consulte Usar lógica combinatoria en código de procedimiento para controlar la salida de síntesis).

Tabla de contenido

Proceso de síntesis básico

Básicamente, las herramientas de síntesis de hardware hacen tres cosas:

- Compile el RTL para crear una representación de hardware de la lógica y los registros de su diseño.

- Traduzca una representación genérica de su diseño a su hardware de destino sin preocuparse por el tiempo. Las herramientas de síntesis generalmente intentan crear un diseño mínimo en este punto.

- Compara las rutas lógicas en el diseño con las restricciones de tiempo y acelera las rutas que fallan en el tiempo. Esto se llama optimización de tiempo.

Comprender estos tres pasos revela uno de los hechos más importantes sobre la síntesis. No crear restricciones de tiempo puede dar como resultado el diseño más pequeño posible, pero es posible que no cumpla con sus objetivos de tiempo.

El proceso de tres pasos también lo ayuda a comprender lo que sucede cuando tiene restricciones de tiempo muy simples. Considere un caso en el que el chip de destino es muy rápido y las rutas son tan cortas que las restricciones de tiempo se cumplen fácilmente. En ese caso, la herramienta de síntesis no detectará las rutas perdidas en el paso 3 y obtendrá el diseño más pequeño posible con el menor tiempo de síntesis.

Comprender estos tres pasos también muestra que restringir en exceso un diseño es peor que no aplicar ninguna restricción de tiempo. Muchas personas piensan en las limitaciones de tiempo de la misma manera que piensan en el acelerador de un automóvil. Cuando presionas el acelerador, el auto trabaja más y va más rápido. Este no es el caso de la composición.

Restringir en exceso el diseño, por ejemplo, estableciendo la restricción al doble de la frecuencia de reloj objetivo, no dificulta el funcionamiento de la herramienta de síntesis. En cambio, la herramienta de síntesis llega al paso 3 y descubre que la mayoría de las rutas no han creado tiempos. El peor infractor, probablemente abordar rutas que no estaban destinadas a hacer tiempos dobles y rendirse antes de probar otras optimizaciones.

¿resultado? Un diseño fuertemente sobre-restringido en realidad tiene peores tiempos que un diseño moderadamente sobre-restringido al 10%. El tiempo será aleatorio. Esto se debe a que las herramientas de síntesis no saben dónde concentrar sus esfuerzos y se rinden al principio del proceso.

Acerca de las restricciones de tiempo

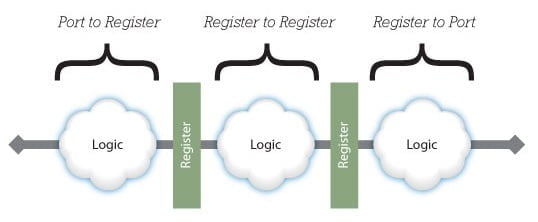

la mayor parte del tiempo [1] , la herramienta de síntesis tiene una visión muy simplista del diseño. Divida todos los diseños en tres pasadas:

- Puertos a registros: esta es la lógica que va desde el pin de entrada del módulo al pin de entrada del primer registro.

- Registros a registros: esta es la lógica que va desde el pin de salida de un conjunto de registros al pin de entrada del siguiente conjunto de registros.

- Registros al puerto: esta es la lógica que va desde los pines de salida del último conjunto de registros al puerto de salida.

Los “puertos” en este diagrama son pines de entrada y salida en un chip o puertos de entrada y salida en un módulo. La composición mostrará lo mismo.

Cuando coloca restricciones de tiempo en su diseño, la herramienta de síntesis convierte las restricciones de tiempo en tres restricciones. Por ejemplo, supongamos que desea que la velocidad del reloj sea de 100 Mhz. La herramienta de síntesis divide esto en tres restricciones:

- Puerto para registrar: 10 ns

- Registro a registro: 10 ns

- Registro a puerto: 10 ns

La restricción de registro a registro de 10 ns es fácil de entender. De particular interés son las restricciones Port to Register y Register to Port. Por ejemplo, suponga que una señal en la placa no llega al chip durante 5 ns. Si la herramienta de síntesis permite una ruta de puerto a registro de 10 ns, no se creará ningún tiempo. La señal llega 5 ns tarde y no está lista para establecerse hasta 15 ns del ciclo de reloj.

Hay dos maneras de lidiar con este problema. Cambie la restricción Port to Register a 5 ns o registre la señal tan pronto como ingrese al chip. Esta es la razón por la que muchos pines de entrada de FPGA tienen registros incorporados.

Tiempo, Jerarquía y Restricciones

Tenga en cuenta que describí las restricciones de entrada y salida como “Puerto para registrar” y “Registrar para puerto” en lugar de “Pin para registrar”. Esto se debe a que es mejor pensar que las herramientas de síntesis se enfocan en un módulo a la vez durante la síntesis. [2].

Este es un artefacto de los requisitos de memoria del análisis de tiempo. El análisis de tiempo puede requerir una gran cantidad de memoria y su uso de memoria crece rápidamente con el tamaño del módulo. Por lo tanto, si la herramienta de síntesis hace referencia a un módulo a la vez, puede manejar diseños grandes sin quedarse sin memoria.

Esto le da una compensación a considerar. Echemos un vistazo al diseño de varios módulos.

En este diseño hay dos módulos con una restricción de 10 ns en la ruta. Mirar un módulo a la vez tiene requisitos de memoria más bajos, pero no entiendo la relación entre la ruta de salida del módulo izquierdo y la ruta de entrada del módulo derecho. Esto puede causar problemas de tiempo.

La solución consiste en decirle a la herramienta de síntesis que “aplane” el diseño. En otras palabras, elimine todos los módulos para crear un módulo grande. Ahora la herramienta de síntesis ve todas las rutas pero usa mucha memoria. Quizás su máquina tiene demasiada memoria.

Las herramientas de síntesis modernas intentan ayudar con esta compensación mediante el aplanamiento selectivo de módulos más pequeños y el uso de algoritmos que pueden considerar la ruta de salida de algunos módulos al examinar las rutas de entrada de los módulos posteriores. Sin embargo, todavía existe una compensación fundamental. Aplanar el diseño brinda la sincronización más precisa, pero puede requerir grandes cantidades de memoria.

Tengo dos consejos.

- Registre las salidas del módulo siempre que sea posible para evitar rutas visibles de registro a salida.

- Deje que la herramienta de síntesis administre la jerarquía del módulo. Si la herramienta determina que el diseño se debe aplanar, aplane el diseño.

Seguir estos dos pasos suele dar los resultados esperados de la herramienta de síntesis.

Resumen y complicaciones posteriores

Este artículo ha explorado algunos de los conceptos básicos de la síntesis y ha explicado cómo crear una netlist que las herramientas de síntesis creen que cumplirá con el tiempo. En el próximo artículo, explicaré cómo esto puede salir mal una vez que la lista de conexiones se ejecuta a través de una herramienta de lugar y ruta, y discutiré cómo garantizar que se cumpla con el tiempo después de que la lista de conexiones se coloque en el FPGA.

[1] Digo “principalmente” porque las técnicas de optimización pueden oscurecer los conceptos de esta sección. No obstante, el concepto aquí está en el corazón de la tecnología de síntesis. Piense en la síntesis en estos términos y estará en el camino correcto.

[2] Algunos han señalado que muchas herramientas de síntesis modernas pueden considerar múltiples módulos a la vez y optimizar a través de los límites del módulo. sí tengo. Pero no todos son posibles, y para comprender las ventajas y desventajas, es más seguro pensar en la composición de esta manera por módulo.