prólogo

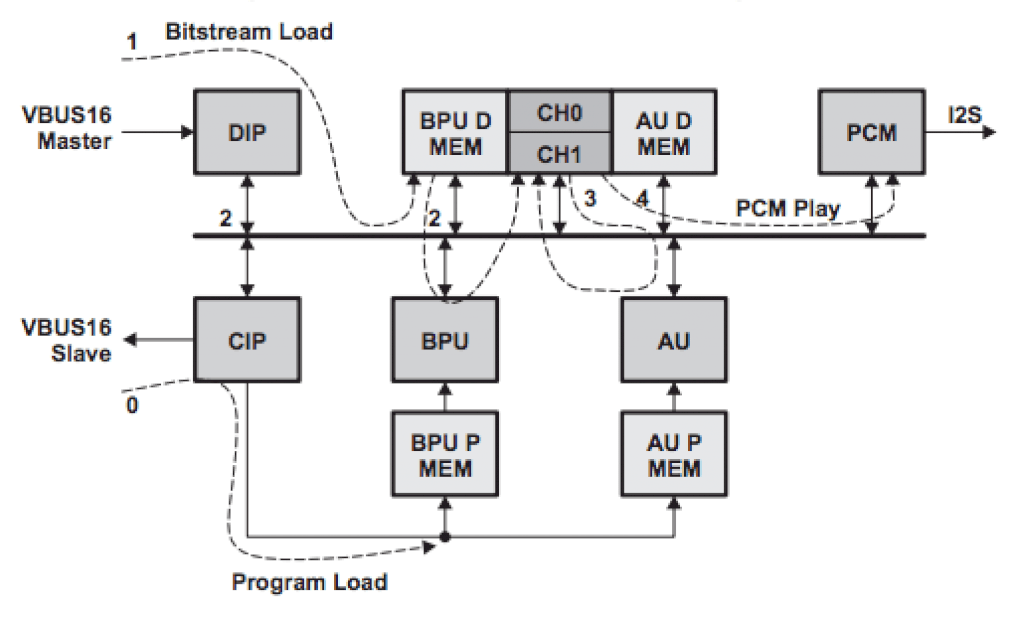

Este documento describe la decodificación de flujo de bits MPEG 1 utilizando el modelo de arquitectura de doble núcleo. La Unidad de procesamiento de bits (BPU) realiza el análisis de flujo de bits y la decodificación de Huffman y actúa como maestro para controlar las Unidades aritméticas (AU). AU realiza operaciones matemáticas intensivas, como la cuantificación inversa, la transformación inversa y los filtros de síntesis.

Este documento consta de tres secciones principales: descripción del hardware, software BPU e interfaz BPU-AU. La descripción del hardware se centra principalmente en la arquitectura de hardware de la BPU. La sección de software BPU describió la arquitectura del software BPU del decodificador de MP3 y el diseño del software de nivel superior.

La interfaz BPU-AU proporcionó información sobre el control y el flujo de datos a través de los diversos módulos de esta arquitectura de coprocesador de audio de doble núcleo, usando el decodificador de MP3 como ejemplo. La arquitectura AU es similar a otras arquitecturas de procesadores de señales digitales (DSP) con funcionalidad limitada para capacidades de procesamiento de audio y requisitos de precisión, por lo que no se describirá en detalle.