Las preocupaciones han existido durante algún tiempo, pero el escalado plano de los circuitos integrados ciertamente se está volviendo más difícil. Incluso si no está de acuerdo con las limitaciones basadas en la física, no se pueden negar los costos adicionales de la litografía de próxima generación (¿cuándo llegará finalmente el EUV?) y el patrón múltiple de capas para lograr tamaños de características más pequeños.

Las preocupaciones han existido durante algún tiempo, pero el escalado plano de los circuitos integrados ciertamente se está volviendo más difícil. Incluso si no está de acuerdo con las limitaciones basadas en la física, no se pueden negar los costos adicionales de la litografía de próxima generación (¿cuándo llegará finalmente el EUV?) y el patrón múltiple de capas para lograr tamaños de características más pequeños. Y no es solo litografía. Otras nuevas tecnologías para poner en marcha la Ley de Moore tienden a ser solo relevantes para una o dos generaciones, lo que las hace más costosas, tanto en costo inicial como en menor retorno de la inversión. Recuerde también que las nuevas estructuras y materiales de transistores más recientes, muy caros e innovadores ya no ofrecen las ventajas de rendimiento y potencia que disfrutó la industria durante el apogeo de la tecnología CMOS.

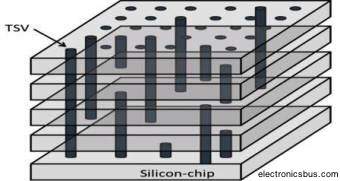

Entonces, ¿el futuro está mirando hacia arriba? Pero espera, dices. La apertura sonaba bastante oscura. Arriba significa 3D. En lugar de meter más dispositivos o más rendimiento en un área de chip determinada, los fabricantes están empezando a tomarse en serio la idea de apilar capas de circuitos integrados una encima de otra, en lugar de reducir el área de cada capa…

Haga clic en el enlace de abajo para leer el resto del artículo.

Apilamiento de circuitos integrados con tecnología de silicio pasante

Este artículo fue enviado por http://www.ingenieria.com