Este informe de aplicación presenta varios métodos para lograr una relación de fase definida entre el reloj de referencia de entrada y el reloj de salida para los búferes de retardo cero basados en PLL de IDT. Este informe se centra en el efecto de diferentes longitudes de seguimiento en los bucles de retroalimentación PLL y el efecto de la carga capacitiva en la entrada del reloj de retroalimentación cuando se genera un reloj temprano (o tardío). El reloj inicial se define como cuando la fase del reloj de salida adelanta al reloj de entrada de referencia.

prólogo

Hay dos tipos principales de arquitecturas de controlador de reloj, el tipo de búfer y el tipo de retroalimentación con un bucle de bloqueo de fase (PLL). En un controlador de reloj con búfer (no PLL), la onda de entrada se propaga a través del dispositivo y es “redirigida” por el búfer de salida. La señal de salida sigue directamente a la señal de entrada con algún retraso de tiempo de propagación del dispositivo (tPD).

Un controlador de reloj de tipo retroalimentación utiliza una ruta de entrada de retroalimentación adicional desde una de las salidas de reloj del dispositivo. Las rutas de retroalimentación pueden ser internas o externas al dispositivo. Para retroalimentación externa, use un trazo en la PCB para conectar el pin de salida al pin de entrada de retroalimentación. Los dispositivos de este tipo generalmente se basan en uno o más PLL que se utilizan para alinear la fase y la frecuencia de las entradas de retroalimentación y referencia. Puede compensar las discrepancias de longitud de seguimiento a nivel de placa para lograr una relación de desviación definida entre los relojes de entrada y salida. La salida se puede dividir, multiplicar o invertir selectivamente mientras se mantiene un sesgo de entrada a salida muy bajo.

¿Qué es PLL?

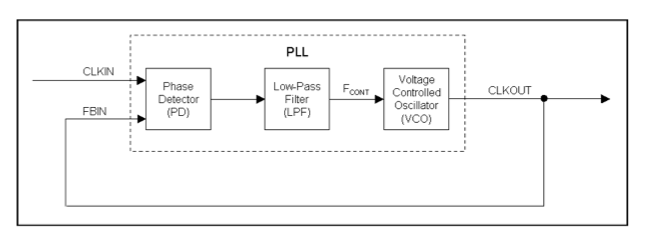

Un PLL básico es un sistema de retroalimentación que recibe una señal oscilante entrante y produce una forma de onda de salida que oscila en múltiplos enteros o fraccionarios de la señal de entrada. Consiste en un detector de fase o frecuencia, un filtro y un oscilador controlado por voltaje como se muestra en la Figura 1. Para que el PLL alinee la entrada de referencia (CLKIN) con la salida, la salida debe retroalimentarse a la retroalimentación. (FBIN) Entrada PLL.

Un detector de fase (PD) normalmente evalúa el flanco ascendente de la entrada CLKIN con respecto a la entrada FBIN. Si la entrada CLKIN adelanta a la entrada FBIN, lo que indica que el oscilador controlado por voltaje (VCO) está funcionando más lento de lo ideal, la PD se “bombea” desencadenada por el flanco ascendente de la entrada CLKIN y continúa hasta el flanco ascendente. Genere una señal . de entrada FBIN. Este pulso de “bombeo” obliga al VCO a funcionar más rápido, lo que reduce la diferencia de tiempo entre las entradas CLKIN y FBIN.

Si la entrada FBIN adelanta a la entrada CLKIN, el PD genera una señal de “bombeo” activada por el flanco ascendente de la entrada FBIN y continúa hasta el flanco ascendente de la entrada CLKIN. El pulso de “bombeo” ralentiza el VCO y reduce la diferencia de tiempo entre las entradas FBIN y CLKIN.