Un bus de interfaz de periféricos en serie es un enlace de comunicación en serie síncrono que funciona en dúplex completo. En otras palabras, los dispositivos envían y reciben datos al mismo tiempo. Los dispositivos se comunican como maestro/esclavo, donde el maestro selecciona un dispositivo esclavo en una línea de hardware para iniciar la comunicación y también proporciona un reloj síncrono que se usa para cambiar los bits de datos dentro y fuera del esclavo.

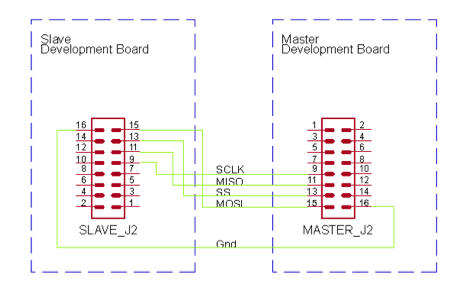

Las señales requeridas para la comunicación son Slave Select (SS), Master In Slave Out (MISO), Master Out Slave In (MOSI) y Serial Clock (SCK). Las ventajas de SPI sobre otros protocolos de comunicación son que el direccionamiento se realiza en hardware utilizando las líneas SS, lo que significa un direccionamiento de dispositivos más rápido, comunicación full-duplex y transferencias de datos más rápidas (Figura 1).

La comunicación SPI comienza cuando el maestro afirma la línea SS. Dependiendo del dispositivo, la línea SS puede estar activa alta o activa baja. Un maestro debe esperar al menos un período de reloj antes de iniciar la comunicación. Al igual que con la polaridad activa de la línea SS, el tiempo de espera después de la activación de SS varía de un dispositivo a otro. Como ejemplo, un convertidor A/D puede requerir que el maestro espere a que se complete la conversión después de que se afirma la línea SS. Luego, el maestro comienza a transferir datos en la línea MOSI y a transferir datos en MISO. Los datos siempre se transfieren como dúplex completo, incluso si los datos no tienen sentido. Por ejemplo, para que el maestro reciba 24 bits de datos del dispositivo esclavo, también debe enviar 24 bits al dispositivo esclavo (Figuras 2 y 3).

Dado que no existe un estándar sobre qué borde de reloj debe usarse para transmitir o recibir datos, existen cuatro posibles modos de operación según la polaridad y la fase del reloj. Consulte la tabla en la Figura 4 a continuación.

Modo SPI

Utilizando el Modo 1 como ejemplo, el maestro baja la línea SCK para dejar el bus en ralentí. Cuando el maestro eleva la línea SCK, el bit más significativo también se coloca primero en la línea MOSI. Al mismo tiempo, el esclavo sitúa su nivel más alto al principio de la línea MISO. Luego, el maestro extrae la línea SCK y lee un bit estable del esclavo en la línea MISO. Al mismo tiempo, el esclavo lee un bit estable generado por el maestro en la línea MOSI. La comunicación finaliza cuando la línea SS se vuelve inactiva, por lo que debe permanecer activa durante todo el marco de comunicación.