descripción general

Una función de encendido/apagado lógico permite al usuario apagar la salida del convertidor mediante una señal lógica TTL simple o un interruptor mecánico, lo que elimina la necesidad de apagar el bus de entrada de CC. Esta función ayuda a hacer circular la potencia de salida sin hacer circular la potencia de entrada. Esto es especialmente útil para la serie μV300 para evitar recargar el límite de almacenamiento de energía de 60 Hz que normalmente filtra el voltaje del bus de 300 V CC.

implementación

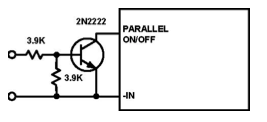

El pin PARALLEL-ON/OFF se utiliza para implementar la función de desactivación. Tirando de la terminal por debajo de 1V @ 4mA con respecto a -IN apagará el módulo.

El pin PARALLEL-ON/OFF se utiliza para implementar la función de desactivación. Tirando de la terminal por debajo de 1V @ 4mA con respecto a -IN apagará el módulo.

Figura 4a Circuito de encendido/apagado lógico que utiliza transistores de señal pequeña.Una señal lógica alta desactiva el convertidor

Figura 4b Circuito de encendido/apagado lógico que utiliza MOSFET de pequeña señal. Una señal lógica alta desactiva el convertidor.

En algunos casos, puede ser deseable desactivar el convertidor utilizando una señal lógica baja. La figura 4c muestra cómo implementar un circuito de desactivación lógica baja.

Figura 4c Circuito de interfaz entre convertidor y lógica TTL. Una lógica baja desactiva el convertidor. Se muestra un ejemplo de μV48 (entrada DC48V).

Los circuitos que se muestran en las Figuras 4a, 4b y 4c son referencias principales. En situaciones donde la señal lógica es la referencia secundaria, se puede usar un optoaislador para desactivar el convertidor, como se muestra en la Figura 4d. Una señal alta desactiva el convertidor.

Nota: La salida del convertidor no se puede utilizar para desactivarse. De lo contrario, el voltaje lógico utilizado para desactivar el convertidor desaparecerá cuando se apague el convertidor, lo que hará que el convertidor se reinicie. Utilice una fuente de alimentación de mantenimiento o varios convertidores paralelos para garantizar los voltajes de las señales lógicas.