Este documento proporciona pautas de diseño de sistemas para una familia de dispositivos de conmutación de interconexión de sistemas que cumplen con la especificación base PCI Express 2.0 de IDT. Este documento también describe las siguientes interfaces de dispositivos y proporciona recomendaciones de diseño de placa relevantes:

Interfaz PCI Express: configuración de puertos

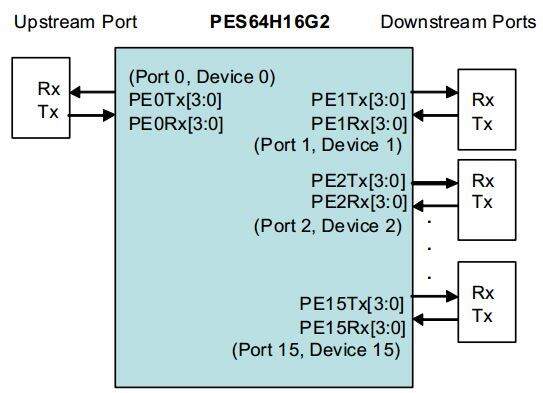

Cada uno de los 16 puertos del PES64H16G2 está asignado estadísticamente a 4 carriles y los puertos están etiquetados del 0 al 15. Por defecto, SWMODE[3:0] = 0x0, el puerto 0 siempre es el puerto ascendente y los puertos restantes son siempre los puertos descendentes. En una configuración de múltiples particiones, SWMOE [3:0] = 0xC, o multipartición con configuración de inicialización de EEPROM serie, SWMOE [3:0] = 0xD, arranque con todos los puertos desconectados. Cualquier puerto puede configurarse como un puerto ascendente o descendente a través de una interfaz EEPROM serial o SMBus esclava. Todos los puertos funcionan con un ancho de enlace máximo de x4 (es decir, 4 carriles) y admiten 2,5 GT/S (Gen1) y 5,0 GT/S (velocidad Gen2).

Circuito de reloj de referencia (REFCLK)

El interruptor tiene dos entradas diferenciales de reloj de referencia global (GCLKP).[1:0]/GCLKN[1:0]) se utiliza para generar todos los relojes necesarios para la lógica del conmutador interno y SerDes. Las entradas de reloj diferencial requieren que la fuente de la señal impulse el modo común de 0 V y la señal REFCLK para cumplir con las especificaciones eléctricas definidas en las Especificaciones electromecánicas de la tarjeta PCI Express. El reloj de entrada de referencia no requiere acoplamiento de CA.

La entrada del reloj de referencia admite el reloj de espectro ensanchado (SSC) para reducir la EMI. Un método necesario es sintonizar la técnica de difusión para que no permita la modulación por encima de su frecuencia nominal. Esta técnica a menudo se denomina “distribución hacia abajo”. Al usar SSC, todos los relojes deben provenir de una sola fuente. Esto incluye el reloj del propio conmutador, el reloj de los dispositivos conectados a los puertos descendentes del conmutador y el reloj del conjunto de chips del complejo raíz u otro dispositivo (conmutador o puente) conectado a los puertos ascendentes del conmutador. Cuando no se usa SSC, se pueden usar múltiples fuentes de reloj para cada dispositivo PCI Express en el árbol.

Los relojes diferenciales para el conmutador y 15 dispositivos aguas abajo se pueden derivar de un búfer/generador de reloj como el ICS9DB803. Los diseñadores de sistemas pueden utilizar otros generadores/búferes de reloj compatibles con Gen2. El dispositivo ICS9DB803 se utiliza en la placa de evaluación IDT.

El conmutador proporciona dos modos de reloj para cada lado del conmutador: reloj global y reloj de puerto local.El diseñador del sistema debe configurar CLKMODE[2:0] Depende de qué modo se seleccione en los lados aguas arriba y aguas abajo del conmutador. Consulte el manual del usuario del dispositivo PES64H16G2, PES48H12G2 o PES32H8G2 para obtener detalles sobre cada modo. El reloj de espectro ensanchado debe estar deshabilitado cuando se usan relojes no comunes en puertos ascendentes o descendentes.

- Esquema de reinicio (reinicio básico)

El pin PERSTN se usa para restablecer toda la lógica en el interruptor y es una entrada de disparador Schmitt que se puede conectar a PERST# desde el sistema o el circuito de reinicio de encendido. En un sistema, los valores de Tpvperi y Tperst-clk dependen del factor de forma mecánico en el que se utiliza el interruptor. Por ejemplo, la especificación electromecánica de la tarjeta PCIe, revisión 2.0, especifica valores mínimos de Tperst-clk=100 µs y Tpvperl=100 ms.