Esta nota de aplicación repasa brevemente la historia del bus I2C. Aquí hay una configuración I2C que ha demostrado facilitar la comunicación entre maestros y esclavos en el bus. Los ejemplos incluyen esquemas y código. El Apéndice 1 contiene definiciones útiles de los términos utilizados en este artículo.

prólogo

El bus Inter IC (I2C) fue desarrollado por Philips Semiconductor a principios de la década de 1980 para reducir la cantidad de líneas de datos paralelas y simplificar los productos electrónicos. La versión 1.0 de la especificación de bus I2C, lanzada por Philips® en 1992, definió un bus bidireccional simple de dos hilos para la comunicación entre circuitos integrados. En 1998, el bus I2C se había convertido en el estándar de facto para la comunicación I2C a I2C de baja velocidad. En ese momento, más de 50 empresas con licencia usaban el estándar y la interfaz I2C se incluía en más de 1000 circuitos integrados diferentes.

La configuración del bus I2C presentada en este artículo ha demostrado que facilita la comunicación con los dispositivos esclavos en el bus. Cada implementación incluye un esquema de ejemplo y un formato de código. Los lectores deben estar familiarizados con los siguientes documentos:

- Especificación de bus I2Cversión 2.1, enero de 2000.

Documento de semiconductores de Philips n.° 9398 393 40011.

- Bus I2C y cómo usarloabril de 1995.

Documento de Philips Semiconductor n.º 98-8080-575-01.

- Especificación del bus de administración del sistema (SMBus)versión 2.0, agosto de 2000.

Antecedentes y consideraciones

El bus I2C puede funcionar en modo estándar, modo rápido o modo de alta velocidad (Hs) con velocidades de datos máximas de 100 kbps (modo estándar), 400 kbps (modo rápido), 1,7 Mbps (modo Hs con Cb = 400pF) y 3,4 Mbps (Modo Hs con Cb = 100pF).

El modo estándar original incorporaba direccionamiento de 7 bits, lo que permitía 112 direcciones esclavas. Como los sistemas de bus I2C requieren más dispositivos esclavos, se introdujo el direccionamiento de 10 bits para asignar más direcciones esclavas.

El modo rápido agregó una función útil para dispositivos esclavos. La velocidad máxima de datos se ha cuadruplicado a 400 kbps. I2C de modo rápido también eliminó el soporte para buses similares que a menudo están vinculados al bus I2C (es decir, buses que ya no son compatibles con velocidades de datos más altas). El dispositivo de modo rápido recibió una entrada de disparador Schmitt para suprimir los picos de ruido. Además, las líneas SCL y SDA del dispositivo esclavo del bus I2C debían presentar una alta impedancia cuando se desconectaba la alimentación.

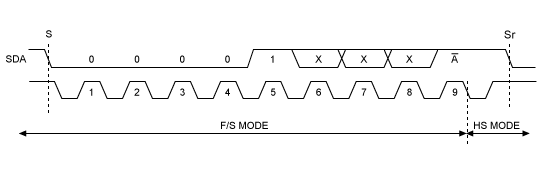

El modo Hs se creó principalmente para mejorar las velocidades de datos y es hasta 36 veces más rápido que el modo estándar. Para el bus I2C que opera en modo Hs, el cambio más significativo afecta la transición de baja a alta de la línea SCL. La mayoría de los sistemas en modo Hs deben incluir un pull-up activo en la línea SCL porque las resistencias de pull-up utilizadas en los modos estándar y rápido no pueden producir tiempos de subida lo suficientemente rápidos para cumplir con la especificación del modo Hs. Otros cambios incluyen solicitudes de compatibilidad de modo Hs emitidas por maestros de modo Hs en modo estándar o rápido usando código maestro de 8 bits. Si Not-Acknowledge (nombre de bit en el marco I2C) permanece alto inmediatamente después del código maestro, toda la comunicación permanece en modo Hs hasta que se detiene. Las formas de onda en la Figura 1 muestran el uso del código maestro para ingresar al modo Hs.

Implementación comprobada de periféricos en chip I2C

El microcontrolador PIC18F442 (µC) incluye un periférico I2C que admite I2C de modo estándar y rápido. La figura 2 muestra un circuito de aplicación que usa ese periférico para adquirir muestras de un ADC de salida en serie de 16 bits (MAX1169). A medida que el PIC® recibe los datos, el firmware UART los transmite inmediatamente a 115 kbaudios. En segundo lugar, un transceptor RS-232 (MAX3232E) permite capturar datos en un puerto serie de computadora personal estándar. Desarrollé el código ensamblador para el circuito de la Figura 2 usando una herramienta llamada MPLAB IDE versión 6.10.00.