prólogo

La interfaz High-Speed Inter-Chip (HSIC) es una interfaz sincrónica de fuente de dos señales capaz de entregar datos USB de alta velocidad a 480 Mbps. Data Transfer es un controlador de host que es 100 % compatible con las topologías USB heredadas. Este formato no admite la velocidad máxima (FS) ni la de baja velocidad (LS), pero los concentradores con HSIC pueden brindar compatibilidad con FS y LS. Las características más importantes de HSIC son:

- Solo la capa física difiere de USB

- Solo datos de alta velocidad, sin protocolo chirp

- Fuente de transmisión de datos en serie síncrona

- Extraíble en caliente/sin conexión, interfaz siempre conectada

- Nivel de señal de 1,2 V diseñado para aplicaciones de baja potencia con niveles LVCMOS estándar

- Longitud máxima de trazo 10 cm

Este documento está escrito para desarrolladores que están familiarizados con el protocolo y las especificaciones USB, pero tienen un conocimiento limitado de la funcionalidad HSIC. El propósito de esta nota de aplicación es familiarizar al lector con HSIC y abordar algunas preguntas comunes relacionadas con la implementación y prueba de aplicaciones HSIC.

Señalización HSIC

La Figura 4 detalla todos los protocolos básicos de señalización de HSIC. Muchas señales como Conectar/Reanudar e Inactivo/Suspender son equivalentes. La Figura 1 muestra la secuencia de conexión (ver también Procedimiento de Conexión) y la Figura 2 muestra el reinicio.

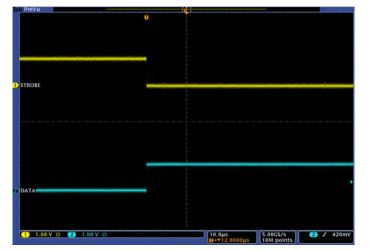

La señalización de datos comienza cuando la luz estroboscópica y las líneas de datos pasan de estar inactivas a terminar inactivas. End-of-Idle se define como la luz estroboscópica que cambia de alto a bajo mientras los datos están bajos. En la Figura 3 se muestra un ejemplo de transferencia de datos del host al dispositivo.

Como se muestra en la Figura 3, el protocolo para las transacciones de datos entre el host y el dispositivo a través de HSIC es el mismo que el de USB. La principal diferencia es que toda la información se envía a través de una sola línea de datos y la señal estroboscópica indica cuándo muestrear la señal de datos recibida. HSIC utiliza señalización de doble velocidad de datos (DDR). Los datos se muestrean en los bordes ascendente y descendente de la señal estroboscópica. La señal estroboscópica oscila a una frecuencia de 240 Mhz, proporcionando una tasa de datos total de 480 Mbps.

Información de la solicitud HSIC

HSIC ofrece varias ventajas notables sobre USB en aplicaciones de chip a chip cableados. HSIC es un estándar completamente digital y no requiere una interfaz analógica. La falta de una interfaz analógica permite un tamaño de troquel más pequeño, lo que reduce el costo. Se pueden hacer ahorros adicionales en troqueles porque el protocolo de conexión simplificado reduce la cantidad de lógica digital requerida.

El estándar HSIC no reduce inherentemente el consumo de energía, pero eliminar el front-end analógico puede ayudar, especialmente porque los circuitos analógicos no necesariamente escalan uno a uno con los circuitos digitales para reducir el tamaño de las características del proceso, lo que puede conducir a diseños de bajo consumo. El HSIC tiene una potencia especialmente baja cuando está en suspensión. No fluye corriente a través de la luz estroboscópica o las líneas de datos durante la suspensión. En comparación, el USB estándar consume un mínimo de 200 μA en D+ a través de una resistencia pull-up de 1,5 kΩ cuando está suspendido.

HSIC difiere de USB solo en la capa física, por lo que pasar de USB a HSIC no es como cambiar a un estándar completamente nuevo. Esto significa que puede migrar rápidamente su pila de software USB existente y su base de conocimientos de protocolo USB a HSIC.