En esta nota de aplicación, para interconectar correctamente varios transceptores ópticos Fast Ethernet de Avago Technologies y varios PHY IC de varios fabricantes seleccionados, se describen las terminaciones necesarias.

En esta nota de aplicación, para interconectar correctamente varios transceptores ópticos Fast Ethernet de Avago Technologies y varios PHY IC de varios fabricantes seleccionados, se describen las terminaciones necesarias.

El acoplamiento de CA se elige como la opción de interfaz general para todos los casos discutidos en esta nota de aplicación debido a su simplicidad en comparación con el acoplamiento de CC. Para el acoplamiento de CA, el diseñador no tiene que preocuparse por la compatibilidad de voltaje de modo común entre la salida del PHY IC y la entrada del transceptor óptico, y viceversa. Conecte y sujete al nivel deseado en el lado de entrada.

Se consideran los siguientes dispositivos PHY IC.

- CI+ IP101G

- Micrel KSZ8041FTL

- Instrumentos de Texas TLK105L

IC+ y Texas Instruments ofrecen circuitos integrados PHY similares con una interfaz de transceptor óptico Fast Ethernet que coincide con los circuitos integrados PHY mencionados anteriormente. Por lo tanto, la terminación descrita en esta nota de aplicación debería funcionar de manera similar a estos otros PHY IC. Consulte la sección Circuitos integrados PHY compatibles al final de este documento para obtener más detalles.

Las interfaces (terminaciones) definidas en esta nota de aplicación han sido evaluadas a temperatura ambiente utilizando el generador y analizador de tráfico Spirent Fast Ethernet. La carga útil de PRBS7 de la trama Ethernet muestra una pérdida de trama del 0 % en 30 horas de comunicación sostenida.

Número de segundos entre PHY IC y Avago Fast Ethernet Optical Transceiver.Sin embargo, las interfaces propuestas aquí son voltaje, temperatura y

Otros cambios de parámetros.

Por lo tanto, los esquemas que se muestran en esta nota de aplicación son solo recomendaciones y Avago no puede garantizar la funcionalidad y el rendimiento completos. Los diseñadores deben realizar su propia verificación.

AFBR-59E4APZ

Este transceptor óptico tiene entradas y salidas LVPECL. Este dispositivo ya incluye condensadores de desacoplamiento para la interfaz acoplada a CA. Por lo tanto, el único problema que debe considerar el diseñador del circuito es la oscilación de voltaje de la señal que va desde la salida del PHY a la entrada del transceptor óptico y viceversa.

La figura 1 muestra la configuración interna de AFBRR-59E4APZ.

CI+ IP101G

Este PHY IC tiene entradas/salidas LVPECL para comunicarse con un transceptor óptico 100Base-FX externo.

La etapa de salida de LVPECL necesita generar corriente.

en el piso. Esto normalmente se logra colocando dos resistencias de 150 Ω entre tierra y Tx+/Tx- respectivamente. Para el IP101G, estas resistencias se incluyen en el PHY IC, lo que simplifica el diseño de la terminación y permite a los diseñadores de circuitos conectar fácilmente el IP101G a los transceptores ópticos. Por otro lado, las resistencias requeridas para la adaptación de impedancia de 50 Ω de la etapa de entrada también están integradas en el PHY IC. Por lo tanto, la única terminación requerida para este PHY es una resistencia que proporcione el nivel de modo común correcto a la etapa de entrada.

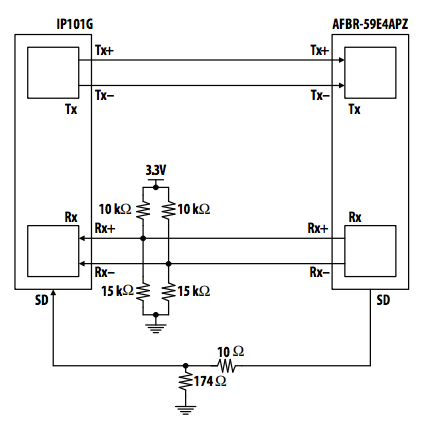

El nivel de modo común requerido por LVPECL es de 2,0 V, por lo que las resistencias que se muestran en la Figura 2 son una buena combinación. Los valores más grandes de estas resistencias dan como resultado que fluya menos corriente a través de estas resistencias, lo que resulta en un menor consumo de energía.

La tabla de la Figura 2 muestra los niveles de voltaje de entrada SD requeridos por el IP101G. Los valores que se muestran en la Tabla 1 y la Tabla 2 permiten configurar el divisor de voltaje adecuado para la conexión SD.

La figura 3 muestra la interconexión de AFBR-59E4APZ e IP101G.

Micrel KSZ8041FTL

Este PHY IC tiene entradas/salidas CML para comunicarse con un transceptor óptico 100Base-FX externo. La etapa de salida del CML se basa en un par diferencial de drenaje abierto que absorbe la corriente que debe suministrarse externamente. Esta corriente normalmente se suministra conectando una resistencia de 50 Ω entre Vcc y Tx+/Tx-. En la etapa de entrada, el KSZ8041FTL requiere un nivel de modo común de aproximadamente 3,3 V. Este nivel de modo común se logra conectando una resistencia de 50 Ω entre Vcc y Rx+/Rx-.

AFBR-59E4APZ tiene entradas y salidas LVPECL. La oscilación de voltaje de la señal en la salida Tx+/Tx- del PHYIC es compatible con la oscilación de voltaje esperada en la entrada Tx+/Tx- del módulo óptico. Además, la oscilación de voltaje de la señal en la salida Rx+/Rx- del módulo óptico es compatible con la oscilación de voltaje que espera el PHY IC en la entrada Rx+/Rx-. Por lo tanto, ambos dispositivos (módulo óptico y PHY IC) se pueden conectar directamente entre sí.

Esto se debe a que el AFBR-59E4APZ está acoplado a CA y contiene las terminaciones correctas dentro de la carcasa (consulte la Figura 2).

Regístrese para recibir el boletín informativo de Avago Now aquí!