Las aplicaciones de red por encima de 25 Tb/s requieren arquitecturas configurables que puedan equilibrar rápidamente los requisitos de potencia, rendimiento y densidad.

Las aplicaciones de red por encima de 25 Tb/s requieren arquitecturas configurables que puedan equilibrar rápidamente los requisitos de potencia, rendimiento y densidad.

puedes recordar eSilicon Proporcionamos IP y ASIC avanzados de clase FinFET a los OEM de sistemas de nivel 1 en los mercados de infraestructura de computación de alto rendimiento, redes, IA y 5G.

Las cosas son muy complicadas cuando se trata de desarrollar ASIC de centros de datos de última generación. Cumplir con los requisitos de potencia, rendimiento y densidad de los ASIC avanzados de clase de red es un gran desafío para los OEM de sistemas. Lo único que puedo decir sobre la creación de un diseño de este tipo y “lanzarlo por la pared” a un proveedor de ASIC que espera recibir un dispositivo listo para la producción en unos pocos meses es una naturaleza optimista.

Para solucionar este problema, el personal de eSilicon administra el diseño, desarrollo y fabricación de ASIC de alta complejidad para sus clientes. Como parte de eso, la compañía anunció una nueva plataforma de red ASIC altamente configurable implementada en una computadora portátil de proceso de 7nm.

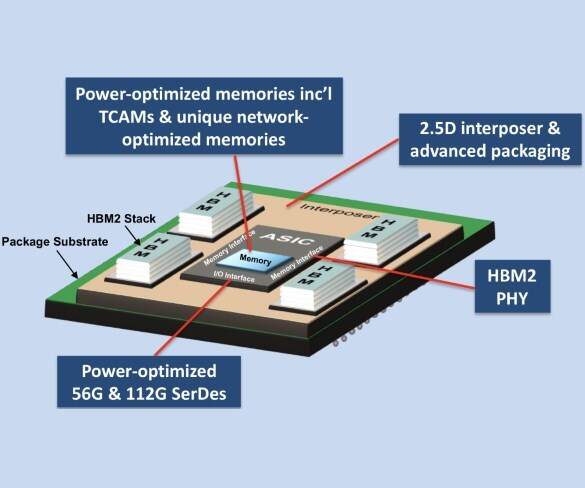

Como se muestra en la figura anterior, esta plataforma combina un ASIC con un número definido por el usuario de pilas de memoria HBM2, todo montado en un intercalador de silicio 2.5D y entregado en un paquete avanzado. Además de la TCAM con optimización de energía y la memoria optimizada para red, el ASIC también incluye un HBM2 PHY y hasta más de 300 canales SerDes de 56G y 112G con optimización de energía.

Además de la IP desarrollada internamente de eSilicon, la plataforma cuenta con IP de socio plug-and-play para funciones como PCI Express PHY, controladores y PLL. Para más información, Sitio web de eSilicon.