Lauro Rizzatti, Experto en Verificación

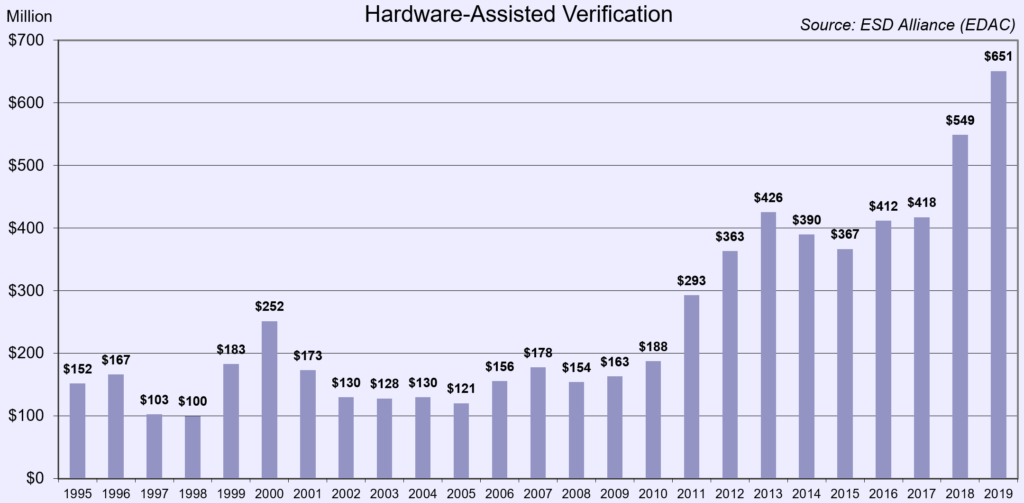

Se proclama que el futuro de la emulación de hardware es impresionante, como lo indica su tendencia ascendente en el desempeño del mercado. Como se reveló en un informe reciente del Servicio de estadísticas de mercado (MSS) de ESD Alliance, los ingresos totales en 2019 superaron los $ 10 mil millones, un aumento del 8.3% con respecto al rendimiento de 2018. La verificación asistida por hardware, que incluye la emulación de hardware y la creación de prototipos de matrices de puertas programables en campo (FPGA), también generó $650 millones en ingresos en 2019 en comparación con $549 en 2018.

Con este aumento del 55%, el último informe de MSS refuerza su creencia de que es probable que esta tendencia continúe en los próximos años. Una mejora adicional de esta garantía es la capacidad de reemplazar el modo de emulación en circuito (ICE). Esto permite el acceso remoto al emulador en modo virtual, eliminando la necesidad de trabajar con adaptadores de velocidad en el laboratorio. Una gran ventaja en la era del coronavirus COVID-19.

Figura 1: ESD Alliance MSS muestra que los ingresos totales superaron los $10 mil millones en 2019, un 8,3 % más que en 2018. [Source: The ESD Alliance]

El MSS de ESD Alliance no tiene una imagen más detallada de estos dos ingresos, pero los ingresos por emulación son más altos, quizás alrededor del 80%. Esto se basa en informes financieros de tres proveedores. Sorprendentemente, esta categoría superó los ingresos de simulación de nivel de transferencia de registro (RTL). Este es un evento histórico y podría ser el tema de una futura publicación de blog.

Las diferencias entre los dos enfoques de validación pueden explicar la gran disparidad en los rendimientos. Desde una perspectiva de 40 000 pies, la emulación de hardware es el uso de la depuración de hardware, la verificación del sistema y la integración de hardware o software (incluida la depuración y los errores de diseño que se propagan por todo el dominio de hardware o software) para crear un sistema en chip (SoC) para verificación previa al silicio de los diseños.

La creación de prototipos de FPGA se centra en la verificación del software integrado y la validación del sistema. Los prototipos también sirven como plataformas de demostración para las primeras muestras de nuevos productos. La emulación requiere fuertes capacidades de depuración a 1-3 MHz, compilación rápida y ejecución rápida. La creación de prototipos de FPGA cambia la capacidad de depuración por la velocidad de compilación en un amplio rango, desde unos pocos megahercios hasta más de 100 megahercios, y depende en gran medida del tamaño del diseño.

La emulación de hardware también supera a otras herramientas de verificación con un modelo de uso muy diverso para numerosas tareas de verificación y aplicaciones prácticamente ilimitadas.

Acelere la Metodología de verificación universal (UVM) para verificar el diseño bajo prueba (DUT) a través de la pila de software, incluidos los controladores, los sistemas operativos y las aplicaciones críticas. Realiza la verificación de baja potencia frente a varios estándares de potencia, genera una base de datos de actividades de diseño para herramientas de estimación de potencia máxima y media, y acelera el análisis de diseño para prueba (DFT). Además, la emulación de hardware admite la cobertura de verificación, las afirmaciones y el análisis de rendimiento.

En resumen, la emulación puede acelerar la verificación del diseño para cualquier diseño, independientemente del tipo o tamaño. Es una buena noticia para el segmento de vanguardia de la industria electrónica, que está creando diseños para 5G, inteligencia artificial (AI) o aprendizaje automático (ML) AI/ML, y aplicaciones de vehículos autónomos, generalmente impulsadas por el tamaño y la complejidad.Excelente.

Todo esto se ejecuta independientemente de la arquitectura de emulación subyacente. De hecho, los tres proveedores de emulación han elegido tres arquitecturas bastante diferentes con sus propias fortalezas y debilidades. Además, la creciente necesidad de emulación de hardware ha llevado a los tres proveedores a diseñar periódicamente versiones más potentes de sus plataformas.

La mayoría de los ingenieros de verificación están de acuerdo en que la emulación de hardware es esencial para mejorar la productividad de la verificación para acelerar el tiempo de comercialización y mejorar la calidad del producto. De hecho, el análisis de retorno de la inversión (ROI) demuestra que la adquisición de herramientas y los costos operativos palidecen en comparación con los ahorros derivados del cumplimiento de los cronogramas de validación y la reducción o eliminación de los nuevos giros de silicio. Sin duda, la emulación es un componente clave de cualquier estrategia de verificación.