Símbolos electrónicos de pestillo y flip-flop

Flip-flops y pestillos son circuitos secuenciales, los componentes básicos de las unidades de memoria. Almacena datos de 1 bit. La salida de un circuito secuencial depende no solo de la entrada actual (actual), sino también de las salidas anteriores.

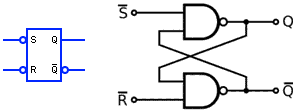

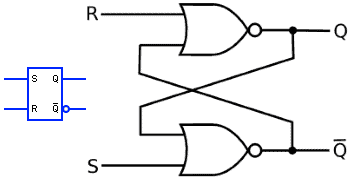

Flip-Flop asíncrono activo-bajo SR NAND

El flip-flop SR, también conocido como pestillo SR, es un circuito secuencial asíncrono (independiente de la señal del reloj) que consta completamente de puertas NAND. SR significa la funcionalidad “set & reset” de un flip-flop.La burbuja de entrada dice que es activa baja.

- Si tanto ‘S’ como ‘R’ están en ALTO, el flip-flop permanece en su estado actual (la salida no cambia).

- Si ‘S’ es BAJO y ‘R’ es ALTO, se establece el estado del flip-flop. Es decir, Q = 1 y Q’=0.

- Si ‘S’ es ALTO y ‘R’ es BAJO, el estado del flip-flop se restablece. Es decir, Q = 0 y Q’=1.

Si tanto ‘S’ como ‘R’ son BAJOS, se dice que el estado no es válido, es decir, la salida es indeterminada. Esta es una condición inválida y será evitada.

| S. | r | estado | qPróximo | Q’ |

| 1 | 1 | Estado de espera (sin cambios) | estado previo | estado previo |

| 0 | 1 | configuración | 1 | 0 |

| 1 | 0 | reiniciar | 0 | 1 |

| 0 | 0 | inválido | X | X |

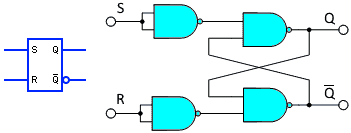

Chanclas SR NAND de alta actividad

Este flip-flop SR se comporta como un flip-flop SR activo-bajo, excepto que la entrada se invierte usando una puerta NAND y un inversor. Esto permite que el flip-flop funcione con una entrada alta activa.

| S. | r | estado | qPróximo | Q’ |

| 0 | 0 | mantener (sin cambios) | estado previo | estado previo |

| 1 | 0 | configuración | 1 | 0 |

| 0 | 1 | reiniciar | 0 | 1 |

| 1 | 1 | inválido | X | X |

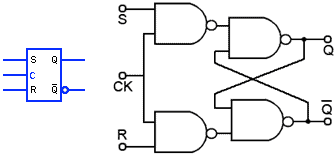

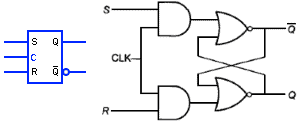

Reloj SR NAND ٖFlip-ٖٖٖٖFlop

| reloj | S. | r | estado | qPróximo | Q’ |

| 0 | X | X | mantener (sin cambios) | estado previo | estado previo |

| 1 | 0 | 0 | mantener (sin cambios) | estado previo | estado previo |

| 1 | 1 | 0 | configuración | 1 | 0 |

| 1 | 0 | 1 | reiniciar | 0 | 1 |

| 1 | 1 | 1 | inválido | X | X |

También conocido como flip-flop SR de reloj o flip-flop SR de puerta, es un flip-flop SR modificado con una entrada de control. Una entrada de reloj controla el estado del flip-flop. Cuando C = 0, el flip-flop SR conserva su estado anterior. En otras palabras, permanece en el estado de espera. Si C = 1, el flip-flop SR se comporta normalmente. Flip-flop alto activo.

Se utilizan para la sincronización con otros circuitos que utilizan una señal de reloj común.

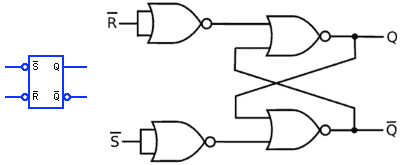

SR NOR Flip-Flop activo bajo

Este flip-flop SR consta de cuatro puertas NOR. Las dos primeras compuertas NOR actúan como inversores para convertir este flip-flop en un flip-flop activo bajo. Una barra en la señal de entrada indica que la entrada está invertida (activa baja).

| S. | r | estado | qPróximo | Q’ |

| 1 | 1 | mantener (sin cambios) | estado previo | estado previo |

| 0 | 1 | configuración | 1 | 0 |

| 1 | 0 | reiniciar | 0 | 1 |

| 0 | 0 | inválido | X | X |

SR NOR Flip-Flop Activo Alto

Este Flip-Flop SR consta de solo dos puertas NOR. Se comporta como un flip-flop SR hecho con compuertas NAND, pero es activo alto.

| S. | r | estado | qPróximo | Q’ |

| 0 | 0 | mantener (sin cambios) | estado previo | estado previo |

| 1 | 0 | configuración | 1 | 0 |

| 0 | 1 | reiniciar | 0 | 1 |

| 1 | 1 | inválido | X | X |

Flip-Flop SR NOR sincronizado

Este es un flip-flop SR cronometrado que usa una puerta NOR. Las puertas AND se utilizan para controlar las señales de entrada. Cuando la señal CLK es ALTA, la señal de entrada fluye y el flip-flop funciona normalmente. Si la señal CLK es BAJA, el flip-flop permanece en espera en la señal S & R.

| reloj | S. | r | estado | qPróximo | Q’ |

| 0 | X | X | mantener (sin cambios) | estado previo | estado previo |

| 1 | 0 | 0 | mantener (sin cambios) | estado previo | estado previo |

| 1 | 1 | 0 | configuración | 1 | 0 |

| 1 | 0 | 1 | reiniciar | 0 | 1 |

| 1 | 1 | 1 | inválido | X | X |

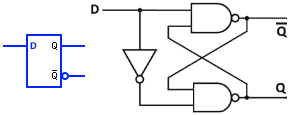

Chanclas D

Los flip-flops D también se denominan flip-flops “DATA” o “DELAY”. Esta es una versión modificada del flip-flop SR con una única entrada común D. Almacena un único bit de datos de la línea de entrada D.

Si D = 0, flip-flop reiniciar & Salida Q es 0. Para D = 1, la salida es configuración & Q se convierte en 1.

| D. | estado | qPróximo | Q’ |

| 0 | reiniciar | 0 | 1 |

| 1 | configuración | 1 | 0 |

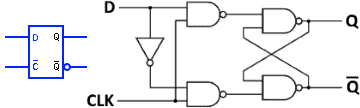

Gated D Flip-Flop (nivel disparado)

Los flip-flops D con compuerta, también conocidos como flip-flops D activados por nivel, tienen una entrada de control adicional llamada entrada de “habilitación” o “reloj”. Cuando CLK = 0, el flip-flop D conserva su estado anterior. Cuando CLK=1, funciona como un flip-flop D normal.

| reloj | D. | estado | qPróximo | Q’ |

| 0 | X | posesión | estado previo | estado previo |

| 1 | 0 | reiniciar | 0 | 1 |

| 1 | 1 | configuración | 1 | 0 |

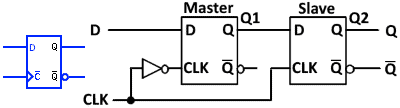

Se dispara el flanco ascendente del flip-flop D

Los flip-flops D activados por flanco también se conocen como flip-flops D maestro-esclavo. Es sensible a los bordes de la señal del reloj y actualiza su valor solo cuando se detecta un borde de reloj.

Puede diseñarse para flancos ascendentes o descendentes. Este es un flip-flop D activado por flanco ascendente.de flanco ascendenteCLK se aplica al flip-flop esclavo Q2 y CLK’ se aplica al flip-flop maestro.

Este flip-flop activado por flanco ascendente actualiza su estado solo en el flanco ascendente de la señal de reloj. Hasta entonces, mantendrá su estado.

| reloj | D. | estado | qPróximo | Q’ |

| X | X | posesión | estado previo | estado previo |

| flanco ascendente | 0 | reiniciar | 0 | 1 |

| flanco ascendente | 1 | configuración | 1 | 0 |

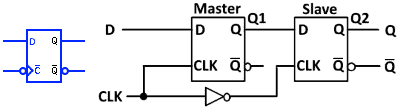

Flanco descendente del flip-flop D disparado

Un flip-flop D activado por flanco descendente actualiza su estado solo cuando hay un flanco descendente en la señal del reloj. El flip-flop conserva su estado anterior hasta el flanco descendente de la señal del reloj.

En un flip-flop activado por flanco descendente, CLK se aplica al flip-flop maestro y CLK’ se aplica al flip-flop esclavo.

| reloj | D. | estado | qPróximo | Q’ |

| X | X | posesión | estado previo | estado previo |

| flanco descendente | 0 | reiniciar | 0 | 1 |

| flanco descendente | 1 | configuración | 1 | 0 |

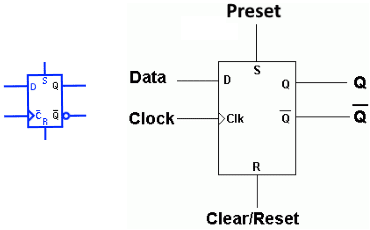

Flip-flop D con preset y clear

Flip-flop D activado por flanco con funciones de preselección (SET) y borrado (reset). Se comporta como un borde que activa D. Las entradas Preset y Clear configuran y restablecen el flip-flop respectivamente (similar al flip-flop SR) independientemente del borde del reloj. Los conjuntos y preajustes se pueden diseñar para entradas activas bajas y activas altas.

| reloj | D. | Preestablecido | claro | estado | qPróximo | Q’ |

| X | X | 1 | 0 | Preestablecido | 1 | 0 |

| X | X | 0 | 1 | claro | 0 | 1 |

| X | X | 0 | 0 | posesión | estado previo | estado previo |

| flanco ascendente | 0 | 0 | 0 | reiniciar | 0 | 1 |

| flanco ascendente | 1 | 0 | 0 | configuración | 1 | 0 |

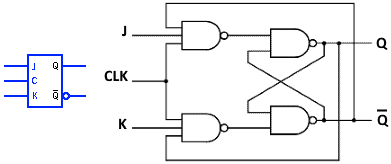

Disparador de alto nivel flip-flop JK

El flip-flop JK es una versión modificada del flip-flop SR. La entrada inhibir (deshabilitar) del flip-flop SR se usa para la función de alternar en el flip-flop JK. Aparte de la función de alternar, las chanclas JK funcionan igual que las chanclas SR.

Este es un flip-flop activado por alto nivel, por lo que si CLK = 1, la señal CLK activará el flip-flop. El flip-flop conserva su estado cuando CLK = 0.

Haga clic aquí para ver la tabla de verdad del disparador de alto nivel del flip-flop JK

| reloj | j | k | estado | qPróximo | Q’ |

| 0 | X | X | mantener (sin cambios) | estado previo | estado previo |

| 1 | 0 | 0 | mantener (sin cambios) | estado previo | estado previo |

| 1 | 1 | 0 | configuración | 1 | 0 |

| 1 | 0 | 1 | reiniciar | 0 | 1 |

| 1 | 1 | 1 | alternar estado | Q’ | q |

Disparador de bajo nivel flip-flop JK

Un flip-flop JK disparado por bajo nivel se activa por el bajo nivel del pulso CLK. Cuando CLK = 0, el flip-flop se activa y actualiza el estado del flip-flop de acuerdo con las entradas J y K. Cuando CLK = 1, la tapa conserva su estado anterior independientemente de las entradas J y K.

| reloj | j | k | estado | qPróximo | Q’ |

| 1 | X | X | mantener (sin cambios) | estado previo | estado previo |

| 0 | 0 | 0 | mantener (sin cambios) | estado previo | estado previo |

| 0 | 1 | 0 | configuración | 1 | 0 |

| 0 | 0 | 1 | reiniciar | 0 | 1 |

| 0 | 1 | 1 | alternar estado | Q’ | q |

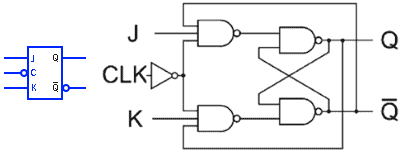

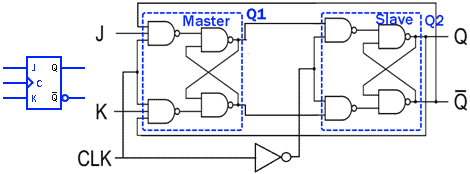

Disparador de borde ascendente de JK Flip Flop

Un flip-flop JK activado por flanco se diseña operando dos flip-flops JK activados por nivel en una combinación maestro-esclavo. Tienen la misma funcionalidad que los flip-flops activados por nivel, excepto que solo están activos cuando hay un borde de reloj.

Un flip-flop activado por flanco ascendente o flanco positivo se activa mediante un flanco ascendente del reloj (0 bajo a 1 alto). Está diseñado con CLK conectado al maestro y CLK’ conectado al flip-flop esclavo.

| reloj | j | k | estado | qPróximo | Q’ |

| X | X | X | mantener (sin cambios) | estado previo | estado previo |

| flanco ascendente | 0 | 0 | mantener (sin cambios) | estado previo | estado previo |

| flanco ascendente | 1 | 0 | configuración | 1 | 0 |

| flanco ascendente | 0 | 1 | reiniciar | 0 | 1 |

| flanco ascendente | 1 | 1 | alternar estado | Q’ | q |

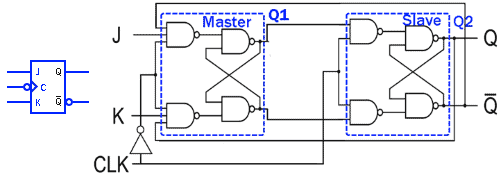

Disparador de borde descendente de flip-flop JK

Un flip-flop JK disparado por flanco descendente es activado por el flanco descendente de la señal de reloj.

En el flip-flop JK disparado por flanco descendente, CLK está conectado al flip-flop esclavo Q2 y CLK’ se aplica al flip-flop maestro Q1. Cuando se detecta un flanco descendente de alto 1 a bajo 0, el flip-flop actualiza su estado de acuerdo con las entradas J y K. De lo contrario, el flip-flop conserva su estado pase lo que pase.

| reloj | j | k | estado | qPróximo | Q’ |

| X | X | X | mantener (sin cambios) | estado previo | estado previo |

| flanco descendente | 0 | 0 | mantener (sin cambios) | estado previo | estado previo |

| flanco descendente | 1 | 0 | configuración | 1 | 0 |

| flanco descendente | 0 | 1 | reiniciar | 0 | 1 |

| flanco descendente | 1 | 1 | alternar estado | Q’ | q |

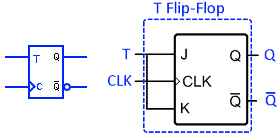

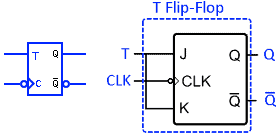

Se activa el flanco ascendente del flip-flop T

El flip-flop T significa flip-flop “toggle” y es una versión modificada del flip-flop JK. Las entradas J y K del flip-flop JK se combinan para formar una entrada ‘T’.

El biestable T cambia de estado cuando T = 1, es decir, Q = Q’. Cuando T = 0, el flip-flop conserva su estado anterior.

Dado que se trata de un flip-flop T de flanco ascendente, el flip-flop solo alterna cuando hay un flanco positivo del reloj, es decir, cuando la señal del reloj va de 0 a 1. De lo contrario, el flip-flop permanece en estado de espera.

| reloj | t | estado | qPróximo | Q’ |

| X | X | mantener (sin cambios) | estado previo | estado previo |

| flanco ascendente | 0 | mantener (sin cambios) | estado previo | estado previo |

| flanco ascendente | 1 | alternar estado | Q’ | q |

Flanco descendente del flip-flop T disparado

Un flip-flop T activado por flanco descendente se crea combinando las entradas (J y K) de un flip-flop JK activado por flanco descendente. Activo cuando se detecta un flanco descendente en la señal del reloj. De lo contrario, el flip-flop conserva su estado anterior independientemente de la lógica de entrada.

| reloj | t | estado | qPróximo | Q’ |

| X | X | mantener (sin cambios) | estado previo | estado previo |

| flanco descendente | 0 | mantener (sin cambios) | estado previo | estado previo |

| flanco descendente | 1 | alternar estado | Q’ | q |

Símbolos eléctricos y electrónicos relacionados: